Junus2012

Advanced Member level 5

Hello friends

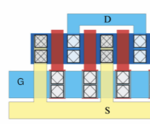

I have 6 transistors (A,B,C,D,E,F) represent the parts of the current mirror in the current mirror amplifier.

D,E,F are five times larger than A,B,C in order to get the factor K=5.

could you please suggest me the array of this mirror in common centroied cross-coupled.

Thank you

I have 6 transistors (A,B,C,D,E,F) represent the parts of the current mirror in the current mirror amplifier.

D,E,F are five times larger than A,B,C in order to get the factor K=5.

could you please suggest me the array of this mirror in common centroied cross-coupled.

Thank you