mburakbaran

Member level 2

- Joined

- Jan 18, 2010

- Messages

- 44

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Location

- leuven

- Activity points

- 1,724

Hi everyone. I'm designing an R-2R DAC which has 8 bits. R=10k. I'd like to make it robust against process gradients. Any ideas on how I can realize that?

I've been checking Baker's book but it did not help me much...

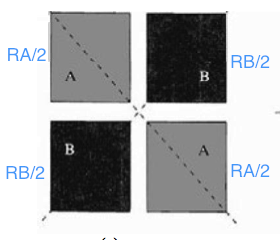

There was this paper mentioning a "Quadrature Layout" technique in which the resistors are split into 4, but they did not give any more details about the implementation of the layout.

Thanks in advance.

I've been checking Baker's book but it did not help me much...

There was this paper mentioning a "Quadrature Layout" technique in which the resistors are split into 4, but they did not give any more details about the implementation of the layout.

Thanks in advance.