Waveco

Newbie level 4

Hello everybody,

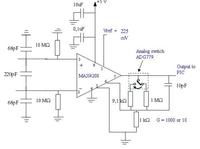

I'm facing some offset problems with an instrumentation amplifier circuit. I'm using it to amplify the 'quasi-DC' signals from a RF detector composed by a dipole antenna and a schottky diode. The schematic is the following:

The connection between the diode and the instrumentation amplifier consists of two resistive lines of 1 MΩ.

I have chosen the MAX4208 instrumentation amplifier as it has very (ultra :wink low input offset voltage (Vios), input bias current (Ib) and input offset current (Ios). Typical specs for 5Vcc and 25 ºC are: Vios = 3 µV. Ib = 1 pA. Ios = 1 pA. Considering these specifications I expected, quite naively, not having any major problem concerning the offset.

low input offset voltage (Vios), input bias current (Ib) and input offset current (Ios). Typical specs for 5Vcc and 25 ºC are: Vios = 3 µV. Ib = 1 pA. Ios = 1 pA. Considering these specifications I expected, quite naively, not having any major problem concerning the offset.

From my calculations, I should have an offset = G * (Vios + Ios*(source impedance/2)). For a G=1000 value: offset = 1000 (3µV + 1pA*(2MΩ + 500kΩ)/2) ≈ 5mV.

However, for a gain = 1000 configuration, I'm getting a negative offset of around 100 mV.

Some clues from the tests I have done:

- For a gain = 10, there is no output offset

- The offset value varies with the resistive lines resistance value.

- The offset shows a great dependence on temperature variations (as a result of scohttky diode junction resistance variation with temperature, I guess)

Any idea on the cause and how to eliminate this offset?

Thank you!

I'm facing some offset problems with an instrumentation amplifier circuit. I'm using it to amplify the 'quasi-DC' signals from a RF detector composed by a dipole antenna and a schottky diode. The schematic is the following:

The connection between the diode and the instrumentation amplifier consists of two resistive lines of 1 MΩ.

I have chosen the MAX4208 instrumentation amplifier as it has very (ultra :wink

From my calculations, I should have an offset = G * (Vios + Ios*(source impedance/2)). For a G=1000 value: offset = 1000 (3µV + 1pA*(2MΩ + 500kΩ)/2) ≈ 5mV.

However, for a gain = 1000 configuration, I'm getting a negative offset of around 100 mV.

Some clues from the tests I have done:

- For a gain = 10, there is no output offset

- The offset value varies with the resistive lines resistance value.

- The offset shows a great dependence on temperature variations (as a result of scohttky diode junction resistance variation with temperature, I guess)

Any idea on the cause and how to eliminate this offset?

Thank you!