The problem:

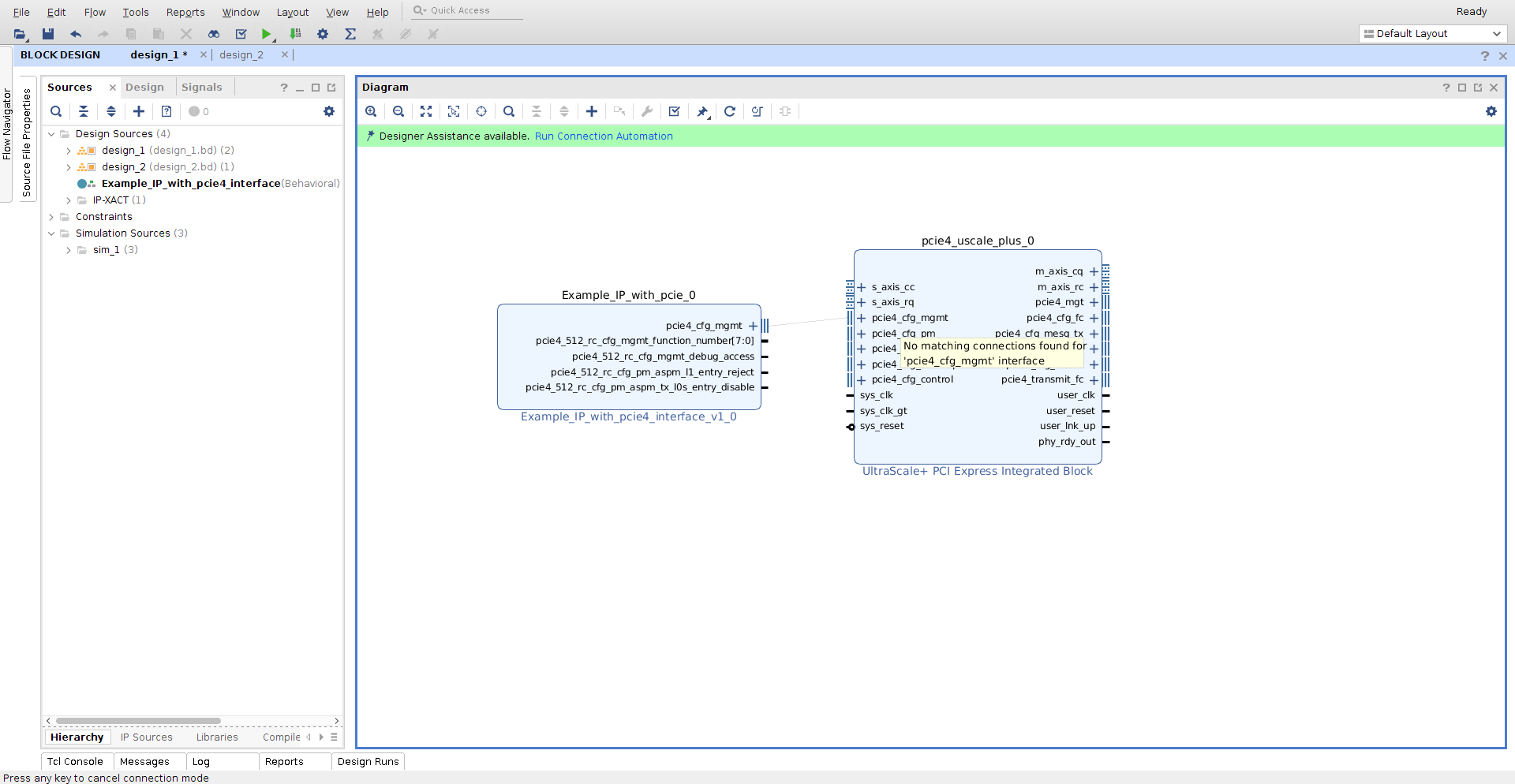

In Vivado in the IP Packager when I was trying to make a custom component with mating interfaces to control PCIe4 IP Core, I couldn't do it because in the IP Packager PCIe4 control interfaces were missing, e.g.:

VLNV xilinx.com:display_pcie4: pcie4_cfg_mgmt_rtl:1.0

VLNV xilinx.com:display_pcie4: pcie4_cfg_pm_rtl:1.0

The only option left for me was to connect every signal in all interfaces one by one.

It would be very time consuming and I would lost the auto-propagation interfaces parameters feature, so I decided to find a workaround.

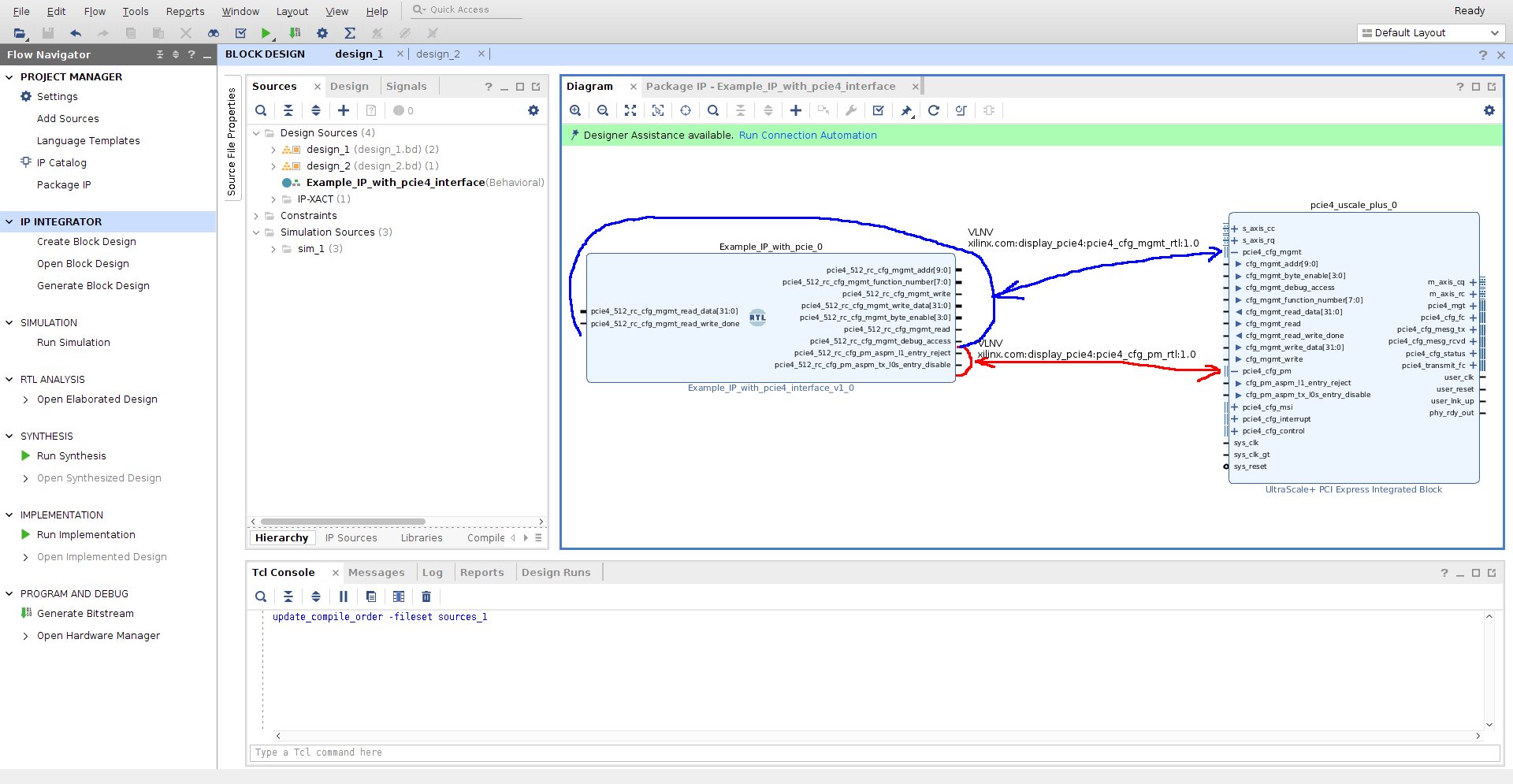

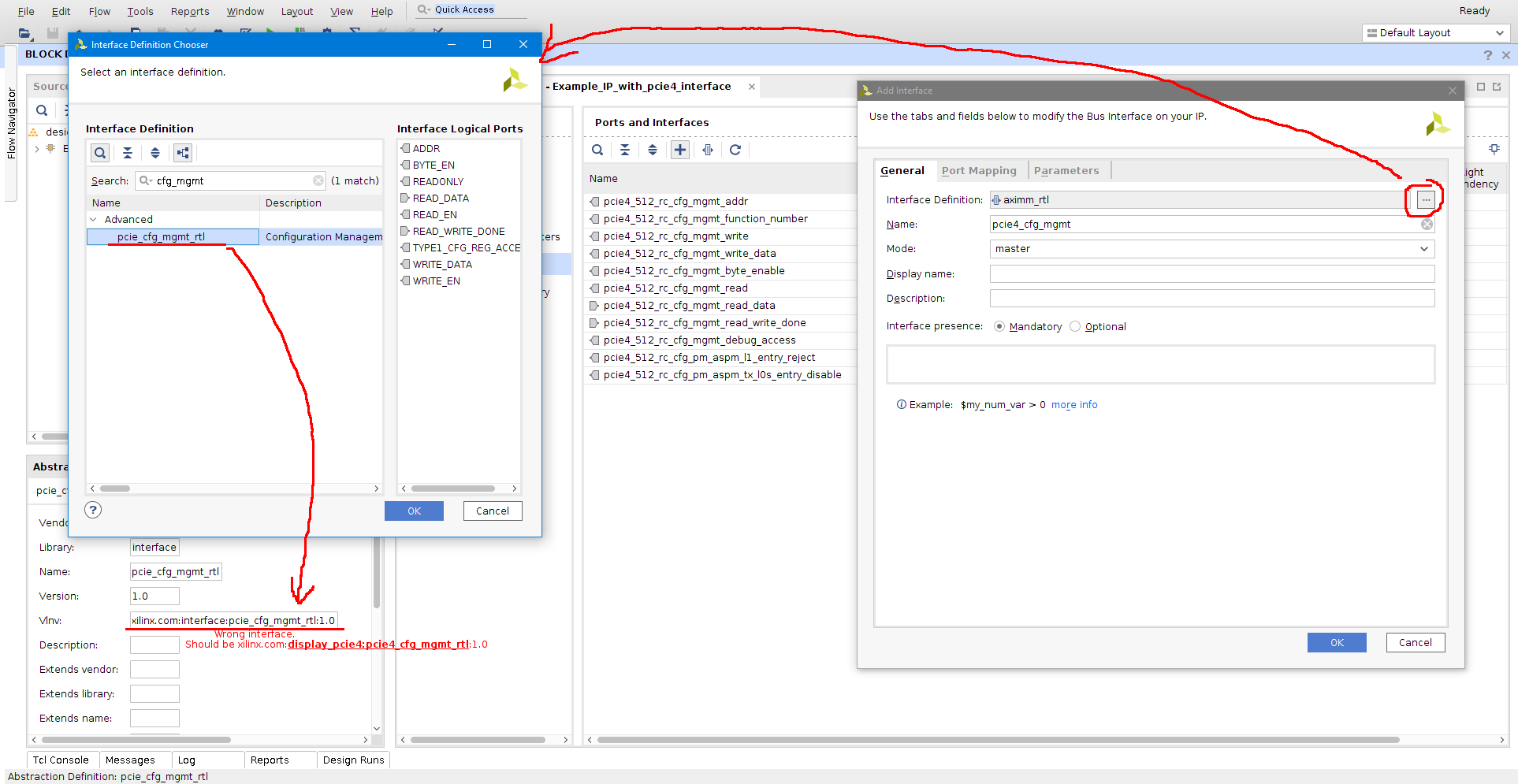

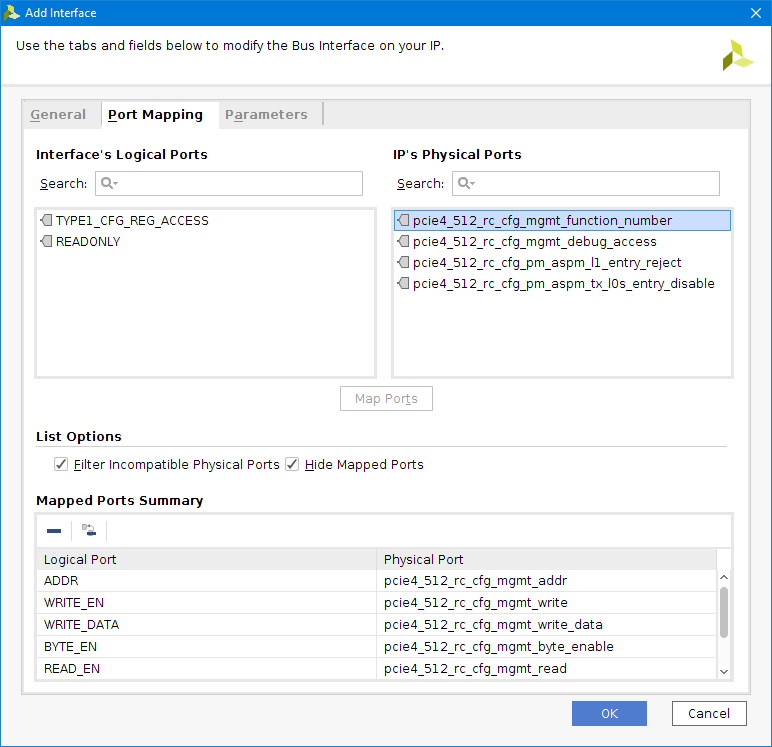

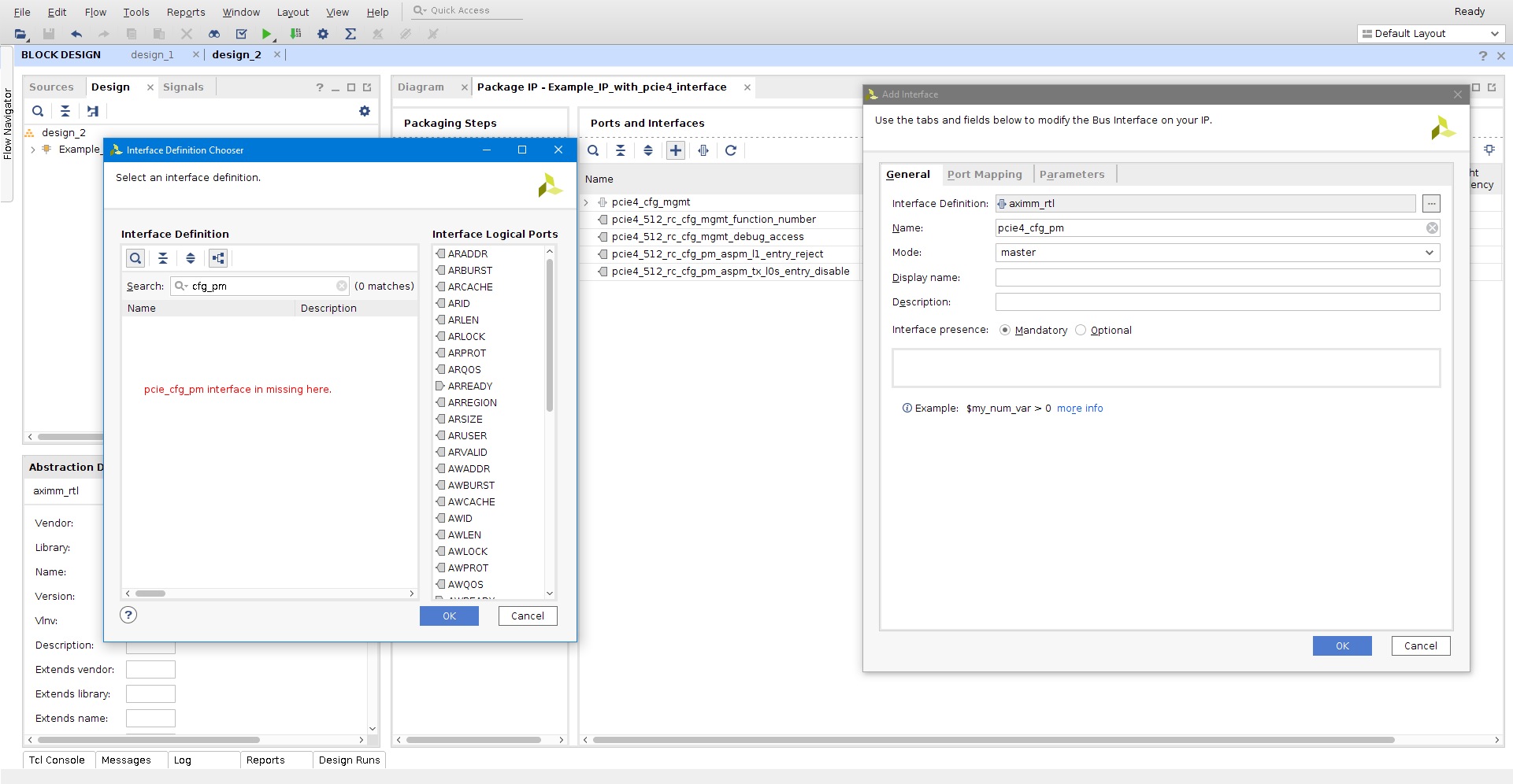

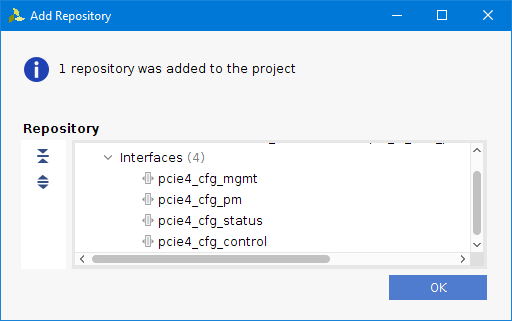

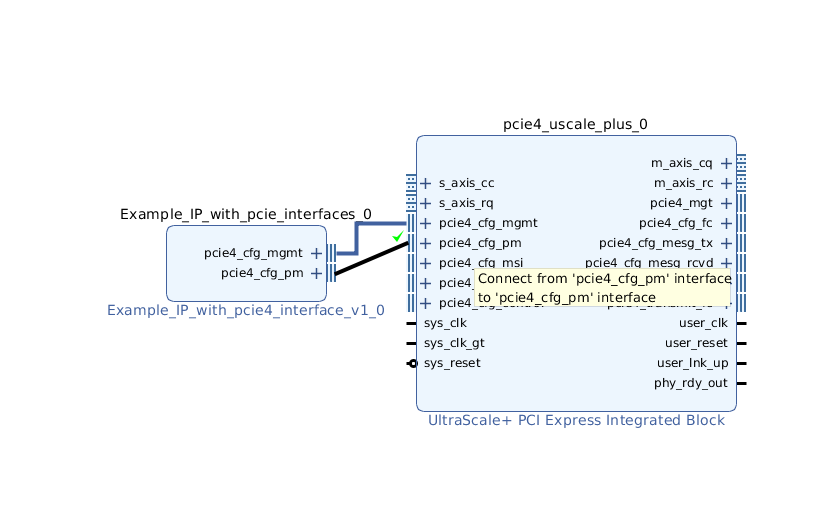

The following pictures visualise the problem:

The solution:

To make a workaround I have copied an “interfaces” folder from the PCIe4 IP Core Vivado installation folder to my project:

<path_to_the_Vivado_installation_folder>/Vivado/<version>/data/ip/xilinx/pcie4_uscale_plus_v1_3/interfaces

I have made modifications to the interfaces as follows:

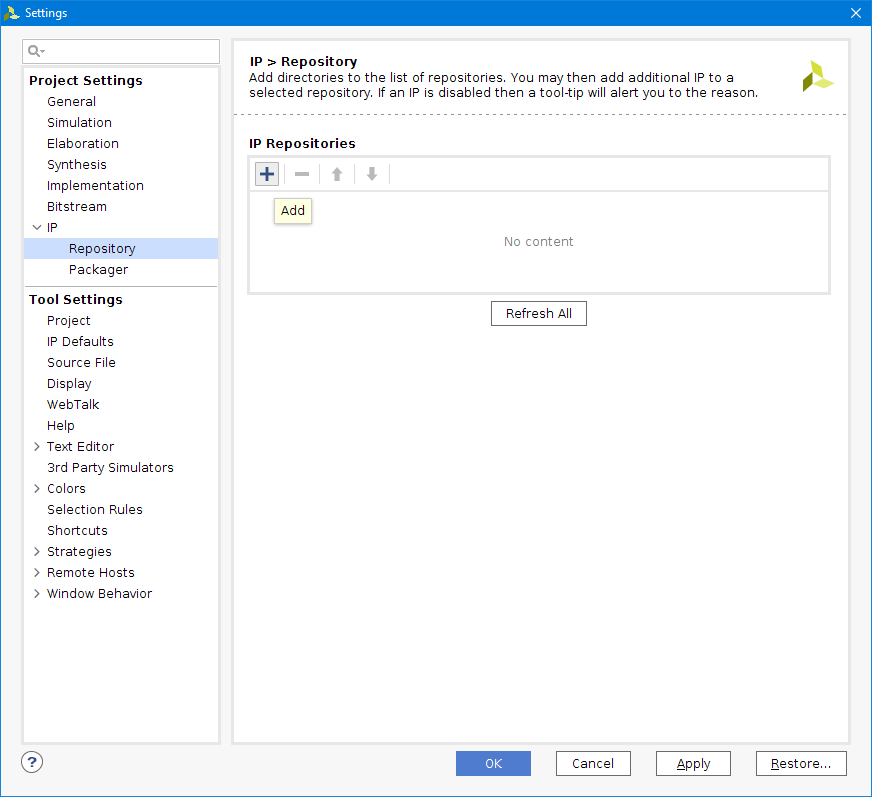

Then I have added changed interfaces folder to my project by Settings->IP->Repository.

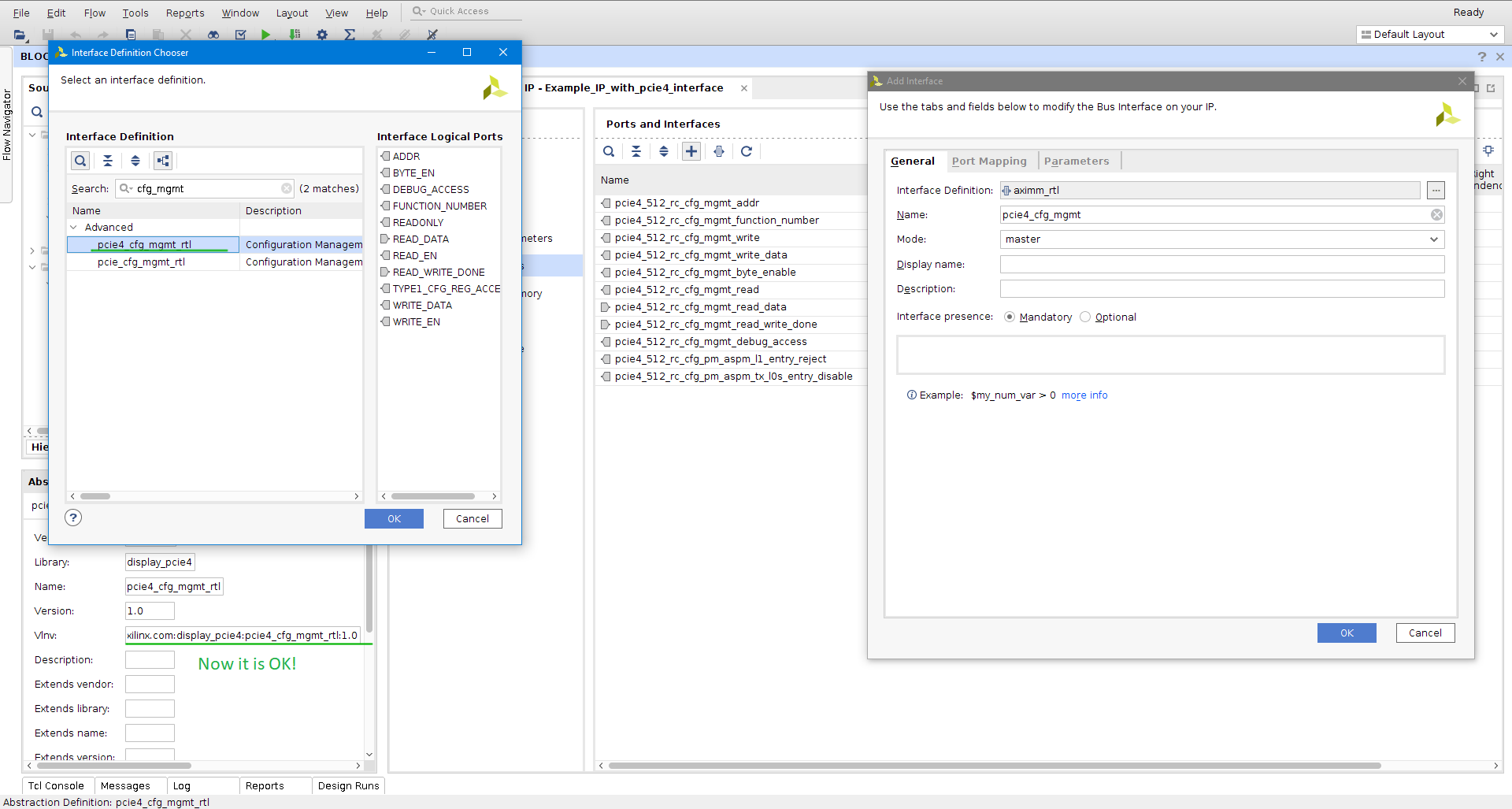

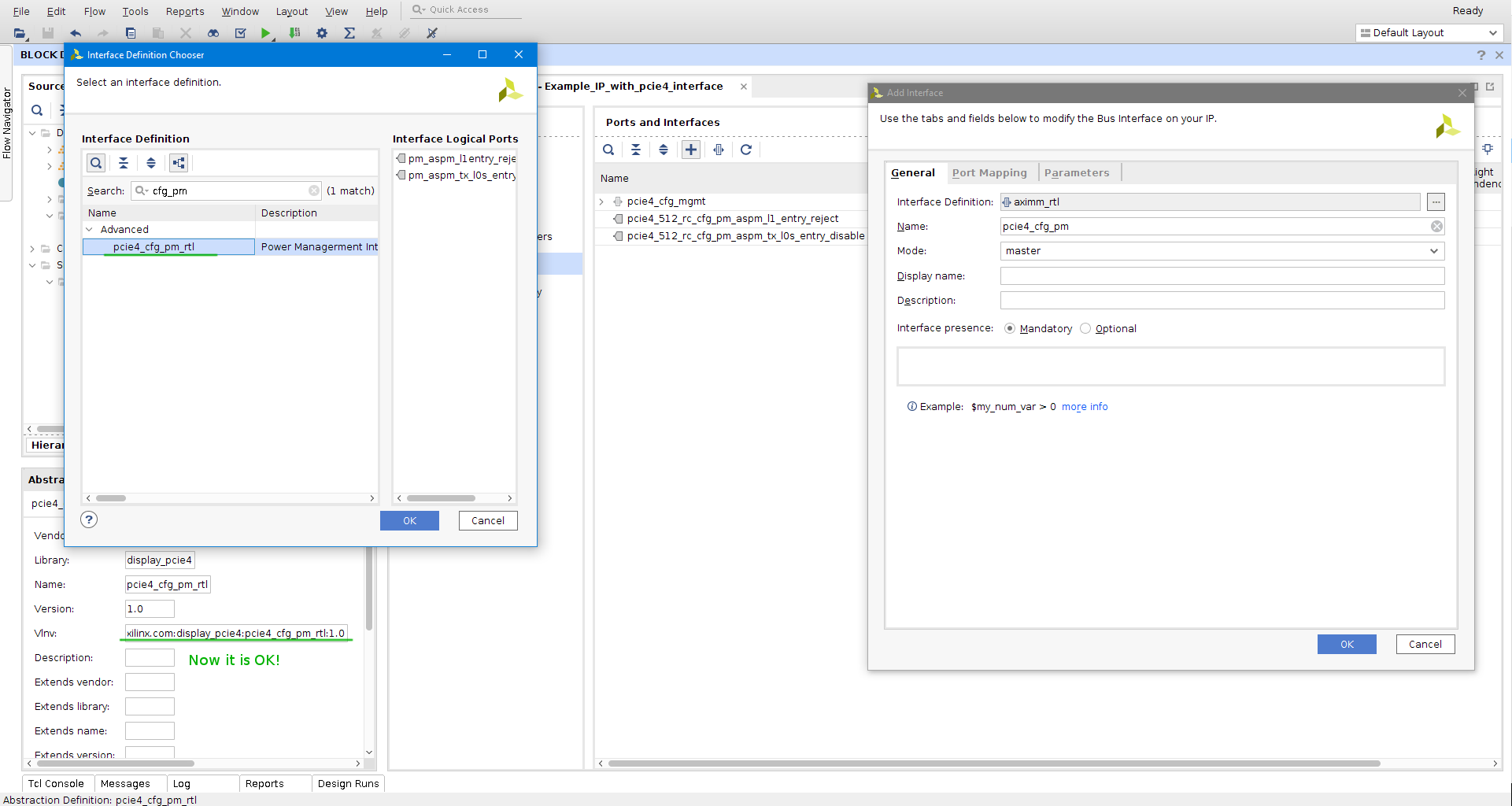

Now I can see and use all PCIe4 interfaces in the IP Packager!

Now I can see and use all PCIe4 interfaces in the IP Packager!

Now the connection of the pcie interface is possible.

------------------------------------------------------

Is this blog entry helpful or does it need an improvement?

Please leave the comment below.

In Vivado in the IP Packager when I was trying to make a custom component with mating interfaces to control PCIe4 IP Core, I couldn't do it because in the IP Packager PCIe4 control interfaces were missing, e.g.:

VLNV xilinx.com:display_pcie4: pcie4_cfg_mgmt_rtl:1.0

VLNV xilinx.com:display_pcie4: pcie4_cfg_pm_rtl:1.0

The only option left for me was to connect every signal in all interfaces one by one.

It would be very time consuming and I would lost the auto-propagation interfaces parameters feature, so I decided to find a workaround.

The following pictures visualise the problem:

The solution:

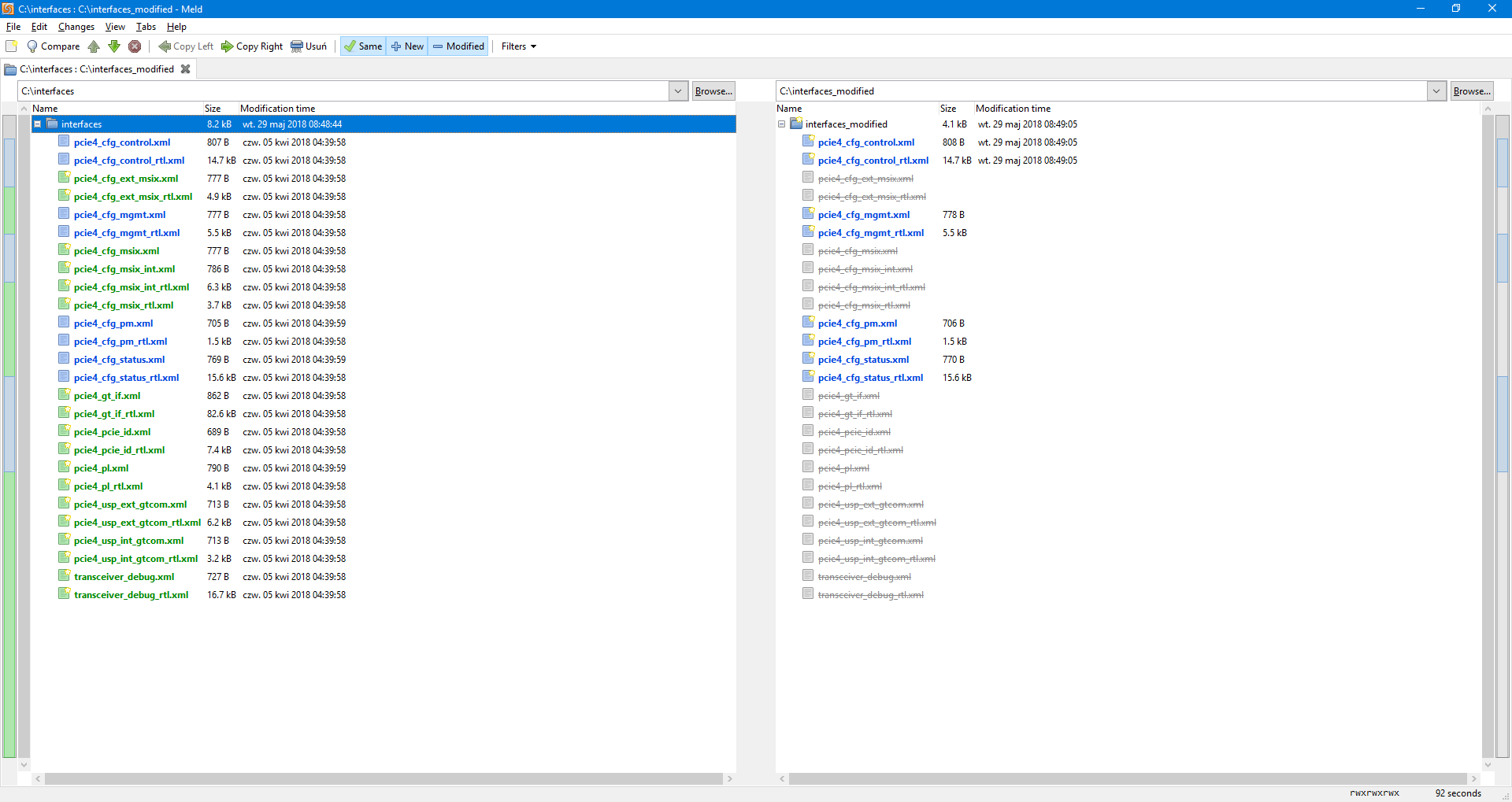

To make a workaround I have copied an “interfaces” folder from the PCIe4 IP Core Vivado installation folder to my project:

<path_to_the_Vivado_installation_folder>/Vivado/<version>/data/ip/xilinx/pcie4_uscale_plus_v1_3/interfaces

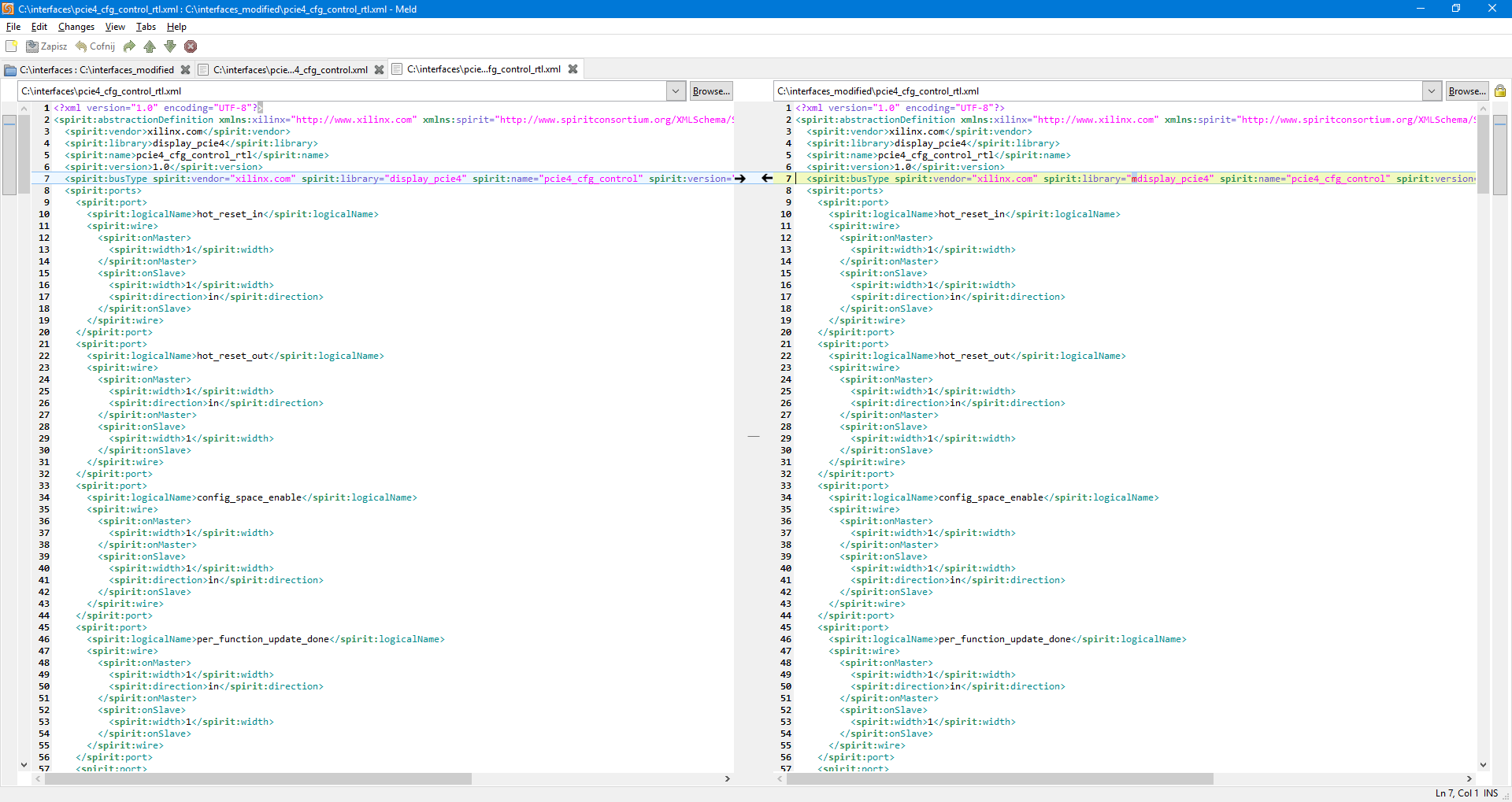

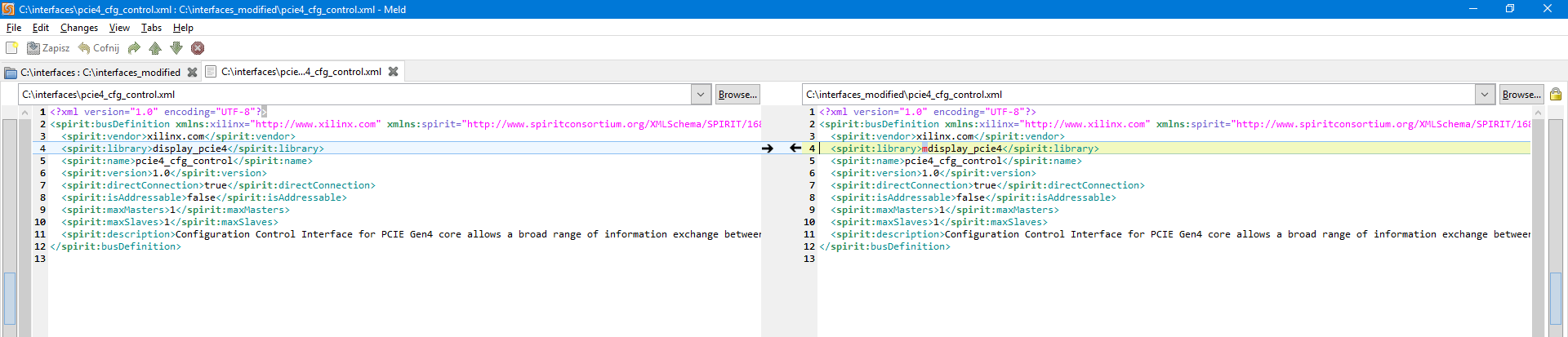

I have made modifications to the interfaces as follows:

- for “*_rtl.xml” files I have added some character, e.g. 'm', at the beginning of the “spirit:busType->spirit:library” parameter value;

- for other xml files I have changed “spirit:library” value parameter accordingly by adding the same character e.g. 'm' at the beginning of the parameter value.

Then I have added changed interfaces folder to my project by Settings->IP->Repository.

Now the connection of the pcie interface is possible.

------------------------------------------------------

Is this blog entry helpful or does it need an improvement?

Please leave the comment below.