The background:

The example solution is focused on the I2C interface.

The walk-through is similar for every single interface.

Adding entry to the board.xml file

Add in <interfaces> section:

Where:

Add in <components> section:

Add in <connections> section:

Adding entry to the pins.xml file

Add in <pins> section

IMPORTANT:

To make these changes work, you must close and reopen project in the Vivado (you don't need to close Vivado, only a project).

Creating the board.xit file

Where:

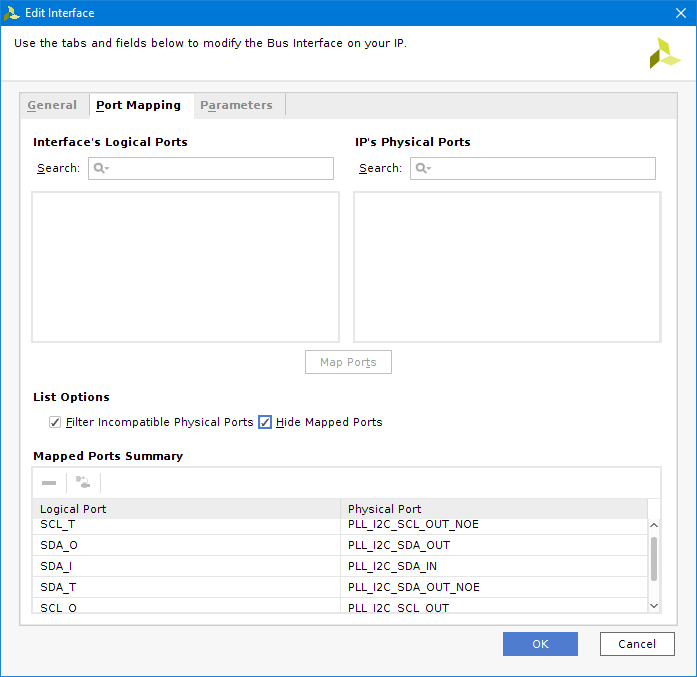

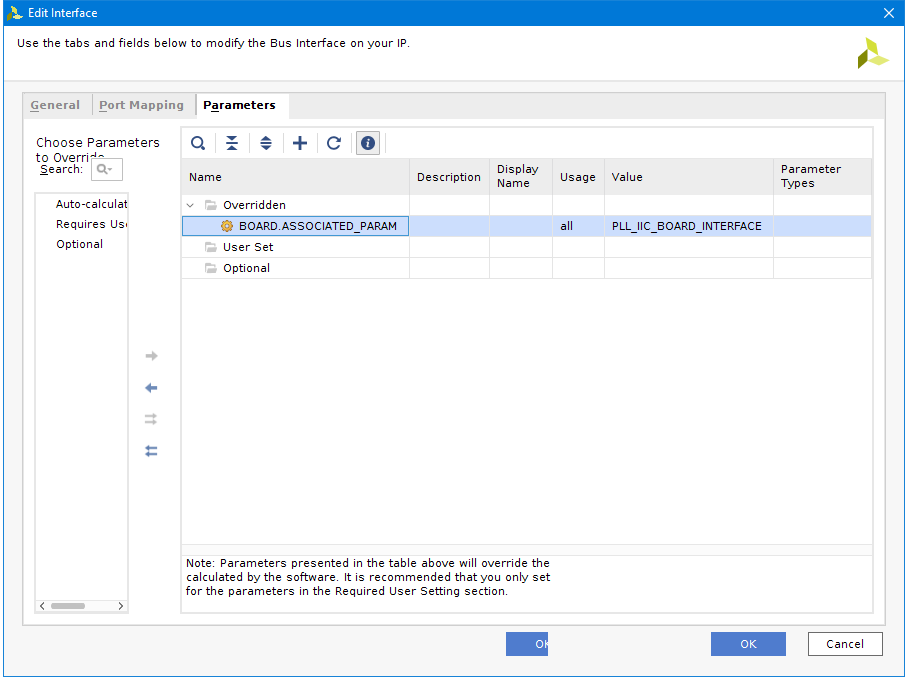

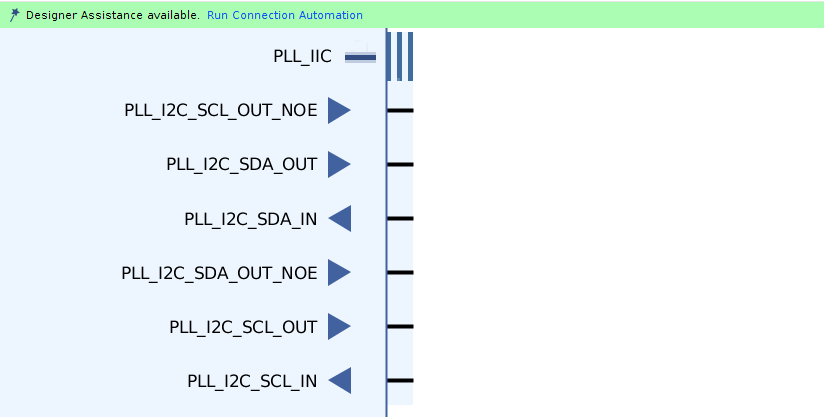

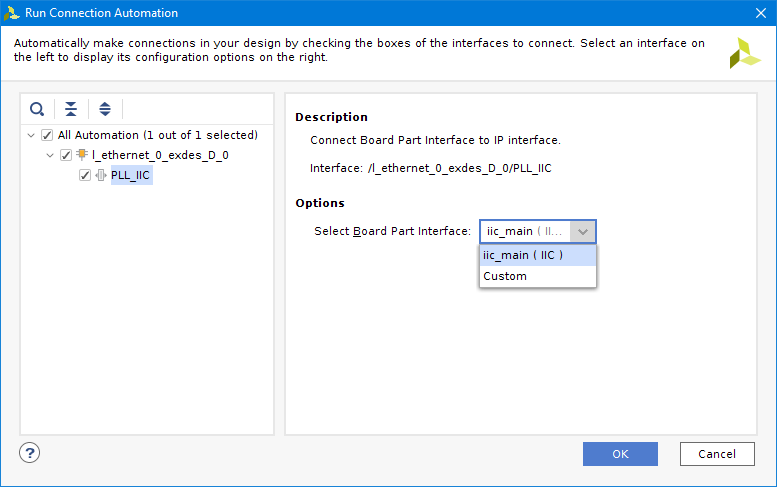

Follow GUI steps

Pack the IP and add it to the Vivado project

Next pack the IP and add it to the Vivado project.

Instantiate or upgrade the IP by calling:

Then follow next GUI steps

Result

After generating Block Design you should get .xdc file in the "$f_xdc" location. The content of the generated .xdc file should be as follows:

The example solution is focused on the I2C interface.

The walk-through is similar for every single interface.

Adding entry to the board.xml file

Add in <interfaces> section:

XML:

<interface mode="master" name="iic_main" type="xilinx.com:interface:iic_rtl:1.0" of_component="iic_main">

<port_maps>

<port_map logical_port="SDA_I" physical_port="iic_main_sda_io" dir="inout">

<pin_maps>

<pin_map port_index="0" component_pin="IIC_SDA_MAIN"/>

</pin_maps>

</port_map>

<port_map logical_port="SDA_O" physical_port="iic_main_sda_io" dir="inout">

<pin_maps>

<pin_map port_index="0" component_pin="IIC_SDA_MAIN"/>

</pin_maps>

</port_map>

<port_map logical_port="SDA_T" physical_port="iic_main_sda_io" dir="inout">

<pin_maps>

<pin_map port_index="0" component_pin="IIC_SDA_MAIN"/>

</pin_maps>

</port_map>

<port_map logical_port="SCL_I" physical_port="iic_main_scl_io" dir="inout">

<pin_maps>

<pin_map port_index="0" component_pin="IIC_SCL_MAIN"/>

</pin_maps>

</port_map>

<port_map logical_port="SCL_O" physical_port="iic_main_scl_io" dir="inout">

<pin_maps>

<pin_map port_index="0" component_pin="IIC_SCL_MAIN"/>

</pin_maps>

</port_map>

<port_map logical_port="SCL_T" physical_port="iic_main_scl_io" dir="inout">

<pin_maps>

<pin_map port_index="0" component_pin="IIC_SCL_MAIN"/>

</pin_maps>

</port_map>

</port_maps>

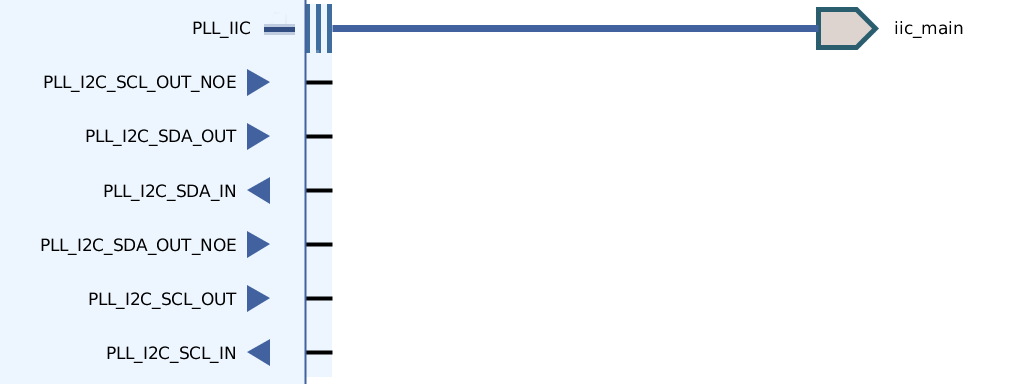

</interface>iic_main - name of the external interface on the Block Design;SDA_I, SCL_I, SDA_O, etc. - logical ports of the xilinx.com:interface:iic_rtl:1.0 interface, all three logical SDA ports are related to one iic_main_sda_io physical port (the same for SCL);iic_main_sda_io, iic_main_scl_io - physical ports that can be found in the elaborated design by viewing it or by typing "get_ports iic_main* in the TCL Console";IIC_SDA_MAIN, IIC_SCL_MAIN - component pins, that will be declared in the pins.xml file later in this solution.Add in <components> section:

XML:

<component name="iic_main" display_name="IIC" type="chip" sub_type="mux" major_group="Miscellaneous">

<description>I2C</description>

</component>Add in <connections> section:

XML:

<connection name="part0_iic_main" component1="part0" component2="iic_main">

<connection_map name="part0_iic_main_1" typical_delay="5" c1_st_index="81" c1_end_index="82" c2_st_index="0" c2_end_index="1"/>

</connection>Adding entry to the pins.xml file

Add in <pins> section

XML:

<pin index="81" name ="IIC_SCL_MAIN" iostandard="LVCMOS18" loc="F15" drive="8" slew="SLOW"/>

<pin index="82" name ="IIC_SDA_MAIN" iostandard="LVCMOS18" loc="G15" drive="8" slew="SLOW"/>IMPORTANT:

To make these changes work, you must close and reopen project in the Vivado (you don't need to close Vivado, only a project).

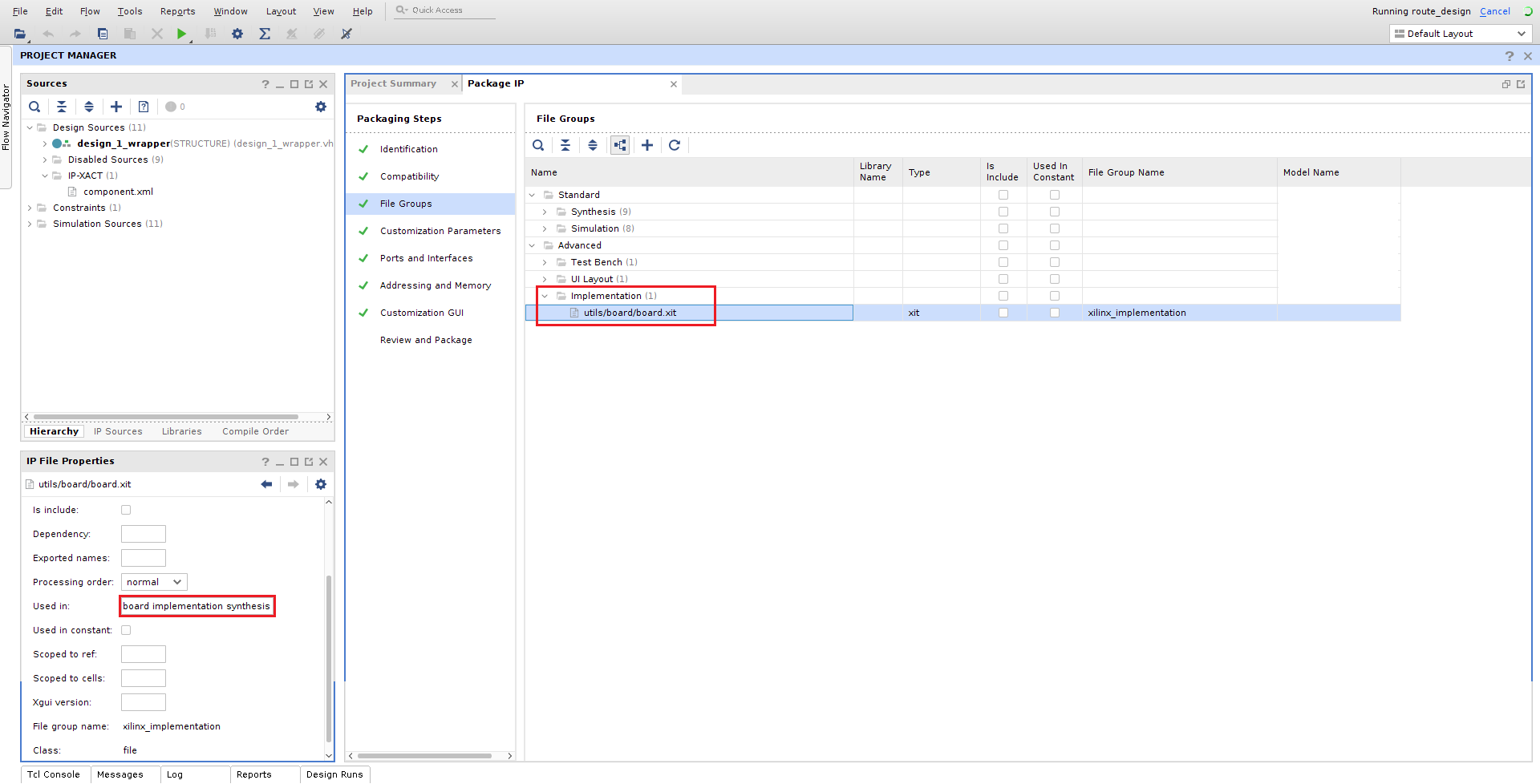

Creating the board.xit file

Perl:

[CODE=TCL]

package require xilinx::board 1.0

namespace import ::xilinx::board::*

set instname [current_inst]

set f_xdc [add_ipfile -usedIn [list synthesis implementation board ] -force ${instname}_board.xdc]

puts_ipfile $f_xdc "#--------------------Physical Constraints-----------------\n"

if {[get_project_property BOARD] == "" } {

close_ipfile $f_xdc

return

}

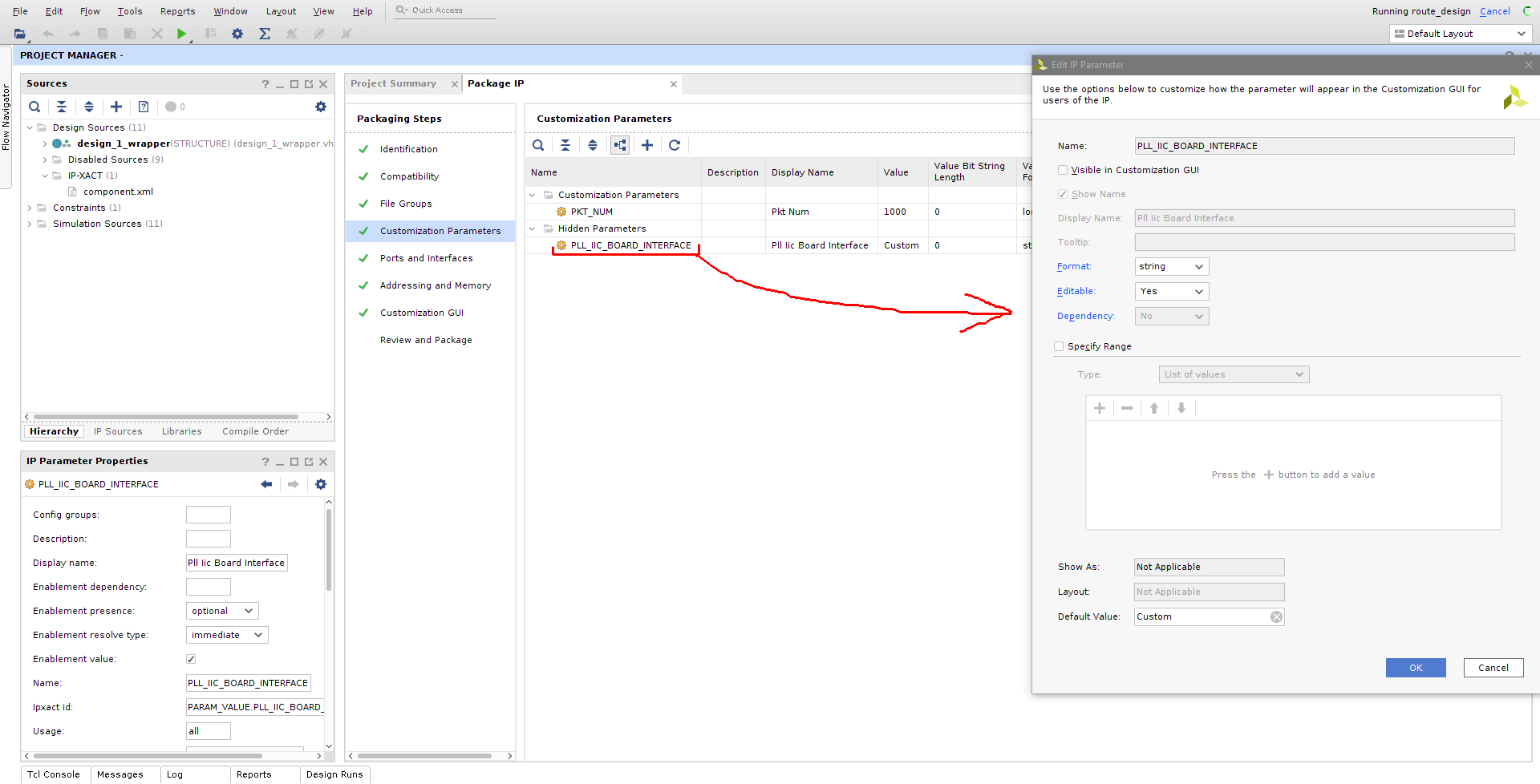

set board_if [get_property PARAM_VALUE.PLL_IIC_BOARD_INTERFACE]

puts "$instname"

puts "$f_xdc"

puts "$board_if"

puts "[get_project_property BOARD]"

if { $board_if ne "Custom"} {

board_add_port_constraints $f_xdc $board_if SCL_I iic_main_scl_io

board_add_port_constraints $f_xdc $board_if SDA_I iic_main_sda_io

}

close_ipfile $f_xdcWhere:

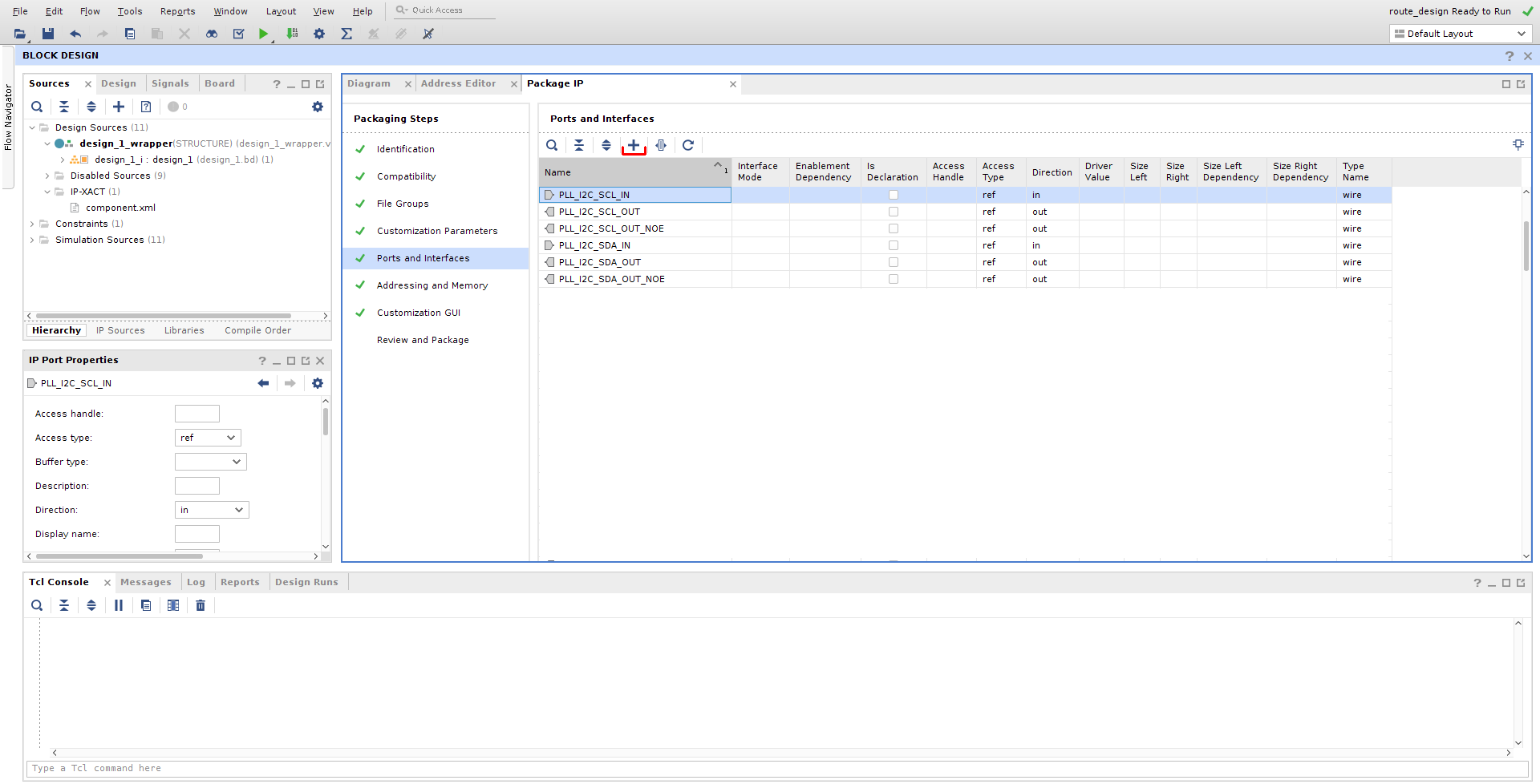

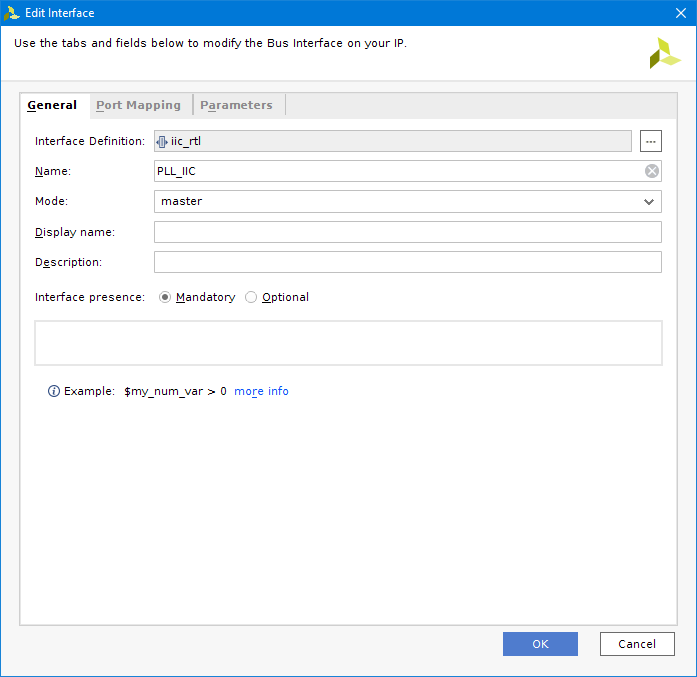

PARAM_VALUE.PLL_IIC_BOARD_INTERFACE - the value of the IP interface BOARD.ASSOCIATED_PARAM parameter;$instname - the current IP instance to generate;$f_xdc - the path and name to the generated .xdc file;$board_if - the name of the IP interface;SCL_I, SDA_I - logical ports of the xilinx.com:interface:iic_rtl:1.0 interface;iic_main_sda_io, iic_main_scl_io - physical ports that can be found in the elaborated design by viewing it or by typing "get_ports iic_main*";board_add_port_constraints - compiled Xilinx's procedure, that I didn't want to decompile and reach.Follow GUI steps

Pack the IP and add it to the Vivado project

Next pack the IP and add it to the Vivado project.

Instantiate or upgrade the IP by calling:

upgrade_ip [get_ips *] in the TCL Console.Then follow next GUI steps

Result

After generating Block Design you should get .xdc file in the "$f_xdc" location. The content of the generated .xdc file should be as follows:

Perl:

#--------------------Physical Constraints-----------------

set_property BOARD_PIN {IIC_SCL_MAIN} [get_ports iic_main_scl_io]

set_property BOARD_PIN {IIC_SDA_MAIN} [get_ports iic_main_sda_io]