SPICE files embody the lowest level of digital and analog circuit behavior in circuit design and verification after place and route. It provides the analog behaviour of transistors and components of digital circuits and gate functions. Multi-layer circuit boards also utilize SPICE, especially if high frequencies are used on the bus. We also now have MEMS, where the SPICE values denote electrical and mechanical components.

In SOC design, SPICE netlists are generated by tools to delineate details of a gate. Transistor geometries and capacitive loads can be used to gauge maximum clock frequency or power consumption. But this SPICE text file is hard to read and understand, since connections come in an onerous long list.

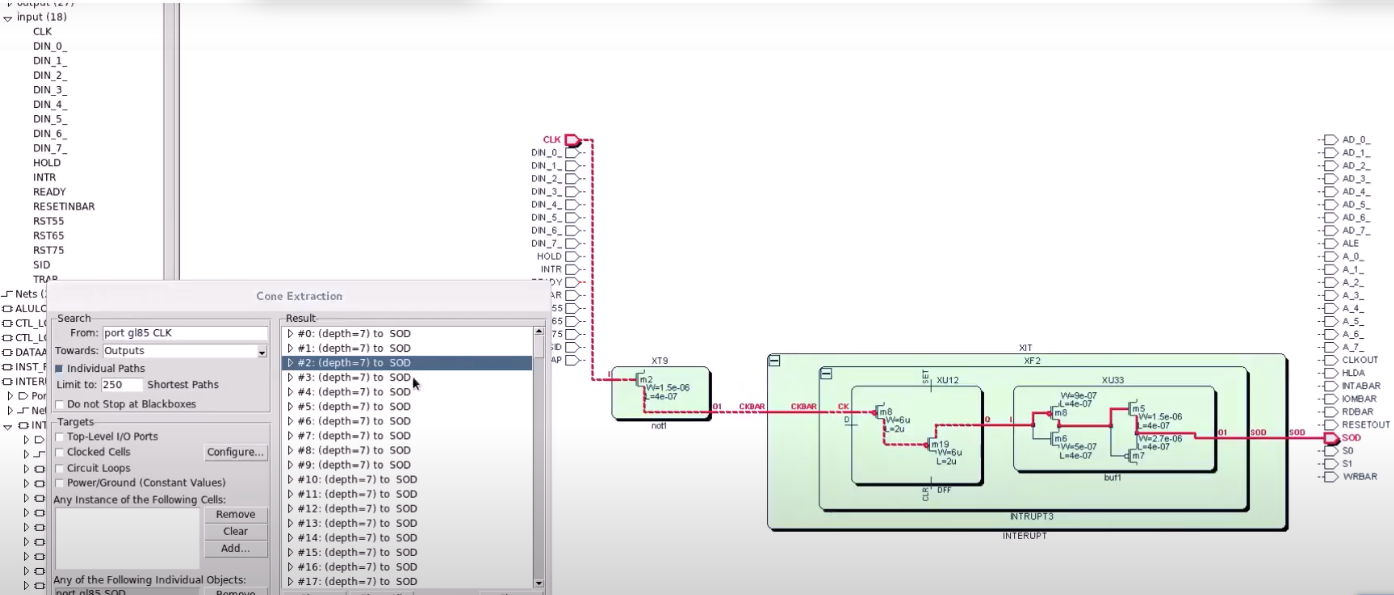

Fortunately now you are able to visualize a SPICE netlist, analyse and debug SPICE models instantly, to optimize the design process. See how you can load a SPICE file, create a circuit diagram automatically, prune and extract paths in this short video with connections and graphical representations of SPICE elements like R, L, C or transistors.

Of course if you have 1000s of transistors you will also want to see an abstract or magnified level of modules and critical paths. This can be achieved through the Cone Window, that can display specific fragments of interest in a new view as a flat or hierarchical design incrementally. These circuit fragments can be transferred to a simulator as separate SPICE netlist files, for partial simulation, often running 10 to 100 times faster than a full simulation. Overall, automatic logic recognition can make design exploration much easier by creating logic schematics from CMOS SPICE-level netlists.

You can also use logic cone extraction in any other analog/mixed-signal design as seen in step-by-step mini videos.

In SOC design, SPICE netlists are generated by tools to delineate details of a gate. Transistor geometries and capacitive loads can be used to gauge maximum clock frequency or power consumption. But this SPICE text file is hard to read and understand, since connections come in an onerous long list.

Fortunately now you are able to visualize a SPICE netlist, analyse and debug SPICE models instantly, to optimize the design process. See how you can load a SPICE file, create a circuit diagram automatically, prune and extract paths in this short video with connections and graphical representations of SPICE elements like R, L, C or transistors.

Of course if you have 1000s of transistors you will also want to see an abstract or magnified level of modules and critical paths. This can be achieved through the Cone Window, that can display specific fragments of interest in a new view as a flat or hierarchical design incrementally. These circuit fragments can be transferred to a simulator as separate SPICE netlist files, for partial simulation, often running 10 to 100 times faster than a full simulation. Overall, automatic logic recognition can make design exploration much easier by creating logic schematics from CMOS SPICE-level netlists.

You can also use logic cone extraction in any other analog/mixed-signal design as seen in step-by-step mini videos.