These days, digital, DFT and mixed-signal engineers have to decipher larger and more complicated System-on-Chip (SoC) functionality, with multiple RTL components and Intellectual Property (IP) blocks obtained from a variety of sources. This can consume hours of engineering time.

Comprehending another engineer's RTL code is not easy, and the right method/tool can make all the difference.

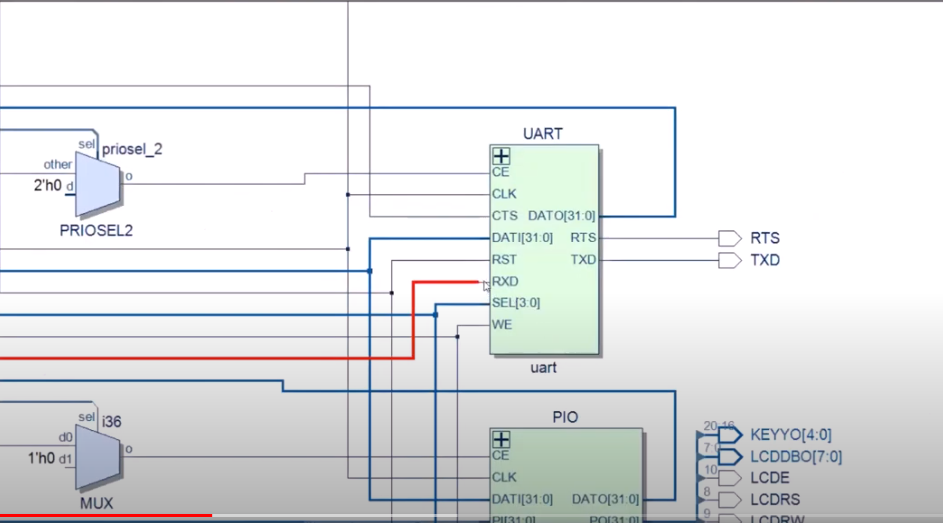

How you can visualize and explore an unknown design and easily convert your Verilog/VHDL/System Verilog netlist to schematics?

See this 4 minute video which shows signal tracing paths in incremental graphical views

You can also check out the free full simple RTL/digital netlist-to-schematics how-to series

Comprehending another engineer's RTL code is not easy, and the right method/tool can make all the difference.

How you can visualize and explore an unknown design and easily convert your Verilog/VHDL/System Verilog netlist to schematics?

See this 4 minute video which shows signal tracing paths in incremental graphical views

You can also check out the free full simple RTL/digital netlist-to-schematics how-to series