Magnethicc

Member level 3

Hi everyone,

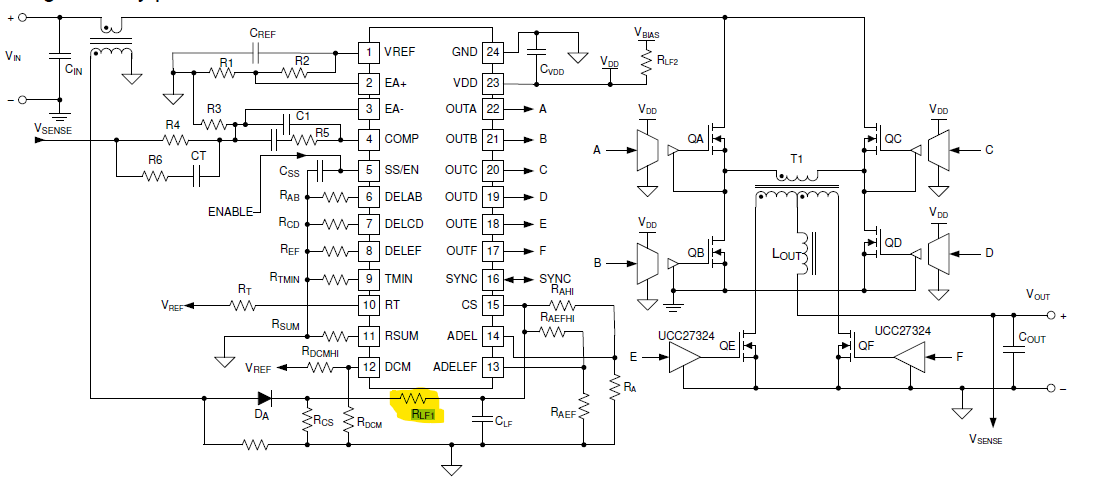

We are doing a high power high current (42V input, 48V output, 5.5kW) PSFB using the UCC28951 and its Adaptive Delay feature. the lead designer wants to use 100Ohms for RLF1 as the filter resistor (of the current sense signal) instead of 1k ohms as stated in the datasheet.

Is there any objections to use 100Ohms instead of 1k?

Thank you!

We are doing a high power high current (42V input, 48V output, 5.5kW) PSFB using the UCC28951 and its Adaptive Delay feature. the lead designer wants to use 100Ohms for RLF1 as the filter resistor (of the current sense signal) instead of 1k ohms as stated in the datasheet.

Is there any objections to use 100Ohms instead of 1k?

Thank you!

Last edited: