yefj

Advanced Member level 4

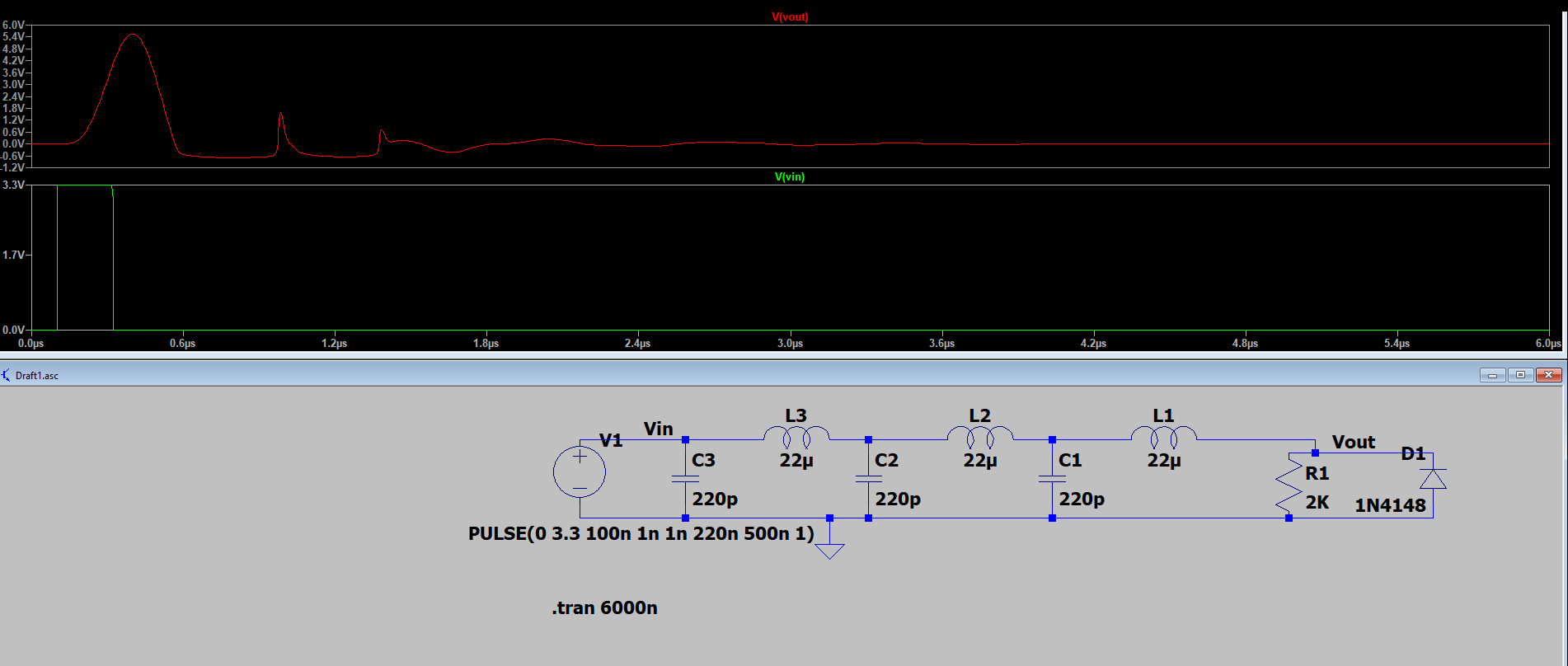

Hello , i was given a schematics which is supposed to be pulse delay .

my pulse is 3.3V and 220nS wide, but instead of a pulse on the outside i get a huge overshoot .

I know that LC system is a differencial equation which can lead to overshoot but its supposed to be a pulse delay.

Where did i go wrong?

LTspice file is attached.

Thanks.

my pulse is 3.3V and 220nS wide, but instead of a pulse on the outside i get a huge overshoot .

I know that LC system is a differencial equation which can lead to overshoot but its supposed to be a pulse delay.

Where did i go wrong?

LTspice file is attached.

Thanks.