wasm

Member level 3

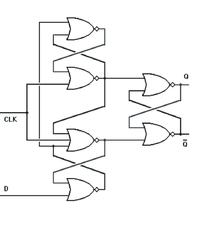

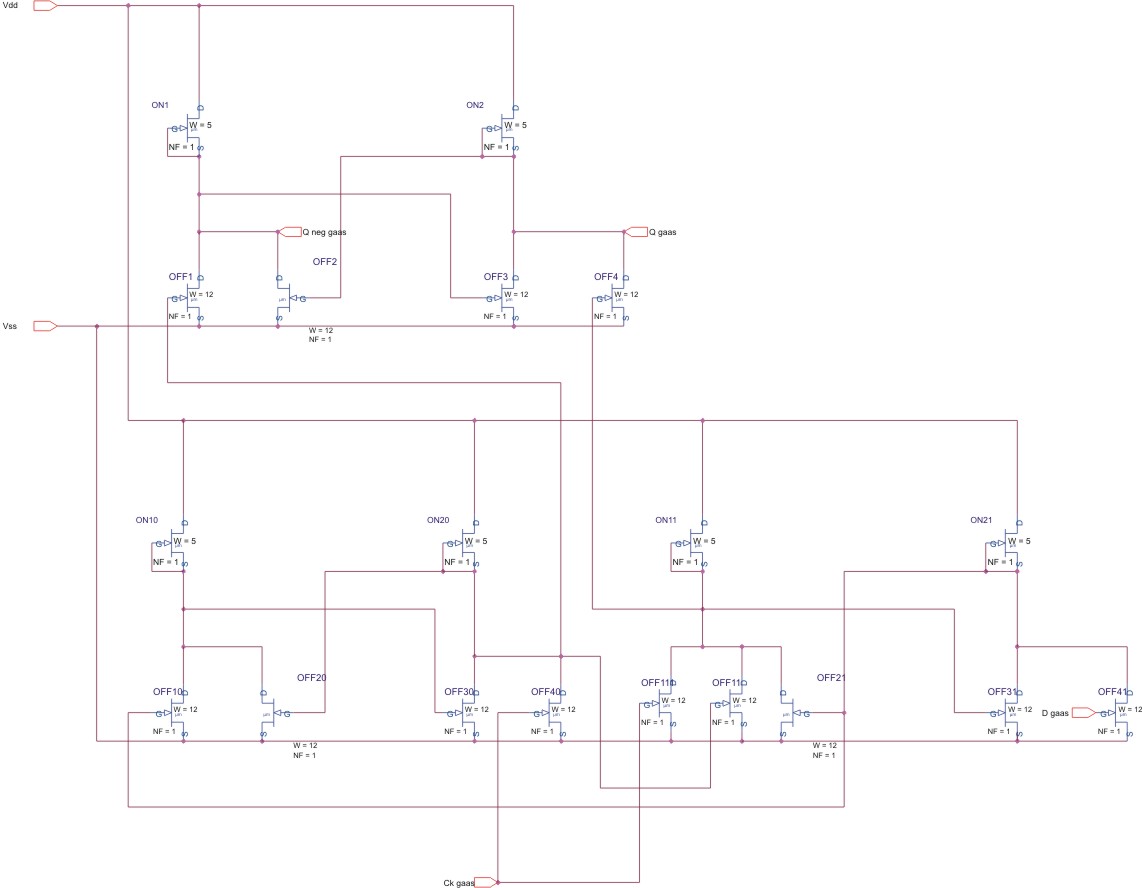

Look at the schematic that follows

There are critical path to consider to avoid that the circuit doesn't works?

Simulations were made without considering interconnecting transission lines, is it a problem? Consider that the speed of the flip-flop is not crucial

There are critical path to consider to avoid that the circuit doesn't works?

Simulations were made without considering interconnecting transission lines, is it a problem? Consider that the speed of the flip-flop is not crucial