chipdesign

Newbie level 4

- Joined

- Aug 24, 2016

- Messages

- 6

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 50

Hi Everyone,

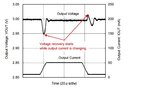

I'm the beginner in the LDO design. I would like understand, what is actually causing the LDO output to have ripples when there is current load switching?

In my simulation test bench, I'm just placing a ideal current load to switch from 0 to 30mA periodically and load cap about 100pF connected to the output of LDO. There is output ripple about 200mVpp whenever the current switching. And when I increase the load cap to 1uF, the output ripples

reduced less than 20mV.

Please help me to understand this.

Thanks

Cheers.

- - - Updated - - -

I do understand the larger external cap suppress the ripples as Xc of the cap reduces providing

low impedance path to gnd for noise filtering. So, in the first place, I need to understand, in every LDO design, what is actually causing the output ripples? V=1R, I=the load current, so which "R" is that contributing to the voltage amplitude.

Thanks

Cheers.

I'm the beginner in the LDO design. I would like understand, what is actually causing the LDO output to have ripples when there is current load switching?

In my simulation test bench, I'm just placing a ideal current load to switch from 0 to 30mA periodically and load cap about 100pF connected to the output of LDO. There is output ripple about 200mVpp whenever the current switching. And when I increase the load cap to 1uF, the output ripples

reduced less than 20mV.

Please help me to understand this.

Thanks

Cheers.

- - - Updated - - -

Hi Everyone,

I'm the beginner in the LDO design. I would like understand, what is actually causing the LDO output to have ripples when there is current load switching?

In my simulation test bench, I'm just placing a ideal current load to switch from 0 to 30mA periodically and load cap about 100pF connected to the output of LDO. There is output ripple about 200mVpp whenever the current switching. And when I increase the load cap to 1uF, the output ripples

reduced less than 20mV.

Please help me to understand this.

Thanks

Cheers.

I do understand the larger external cap suppress the ripples as Xc of the cap reduces providing

low impedance path to gnd for noise filtering. So, in the first place, I need to understand, in every LDO design, what is actually causing the output ripples? V=1R, I=the load current, so which "R" is that contributing to the voltage amplitude.

Thanks

Cheers.