jstefanop

Member level 2

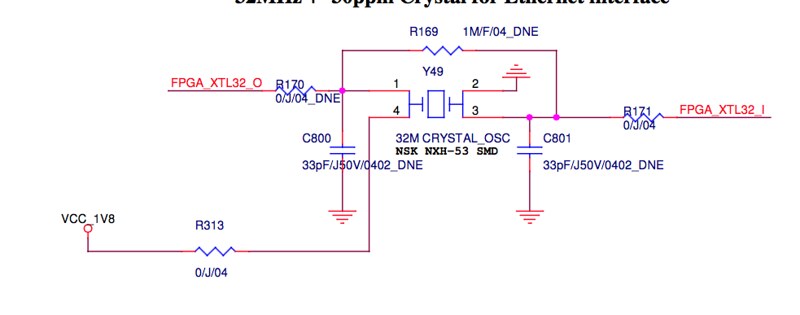

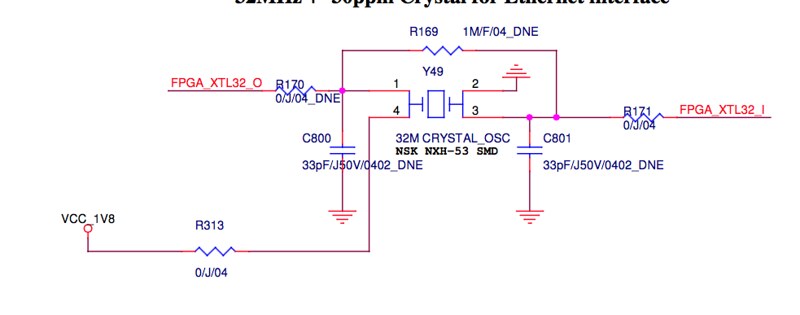

I have a 32MHz crystal clock that I need to connect to PLL Clock input and loopback pins. Current design refrence has the oscillator connected to a Spartan 6 FPGA which then feeds the clock signal to the ASIC chips and is wired like so:

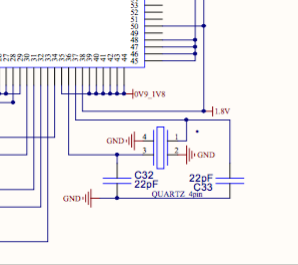

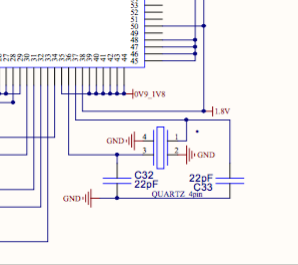

In my design I need a direct connection from the oscillator to the ASIC pins so have it hooked up like so:

Most designs have pin 4 to ground for this clock....so why does the reference design have it hooked up to VCC?

In my design I need a direct connection from the oscillator to the ASIC pins so have it hooked up like so:

Most designs have pin 4 to ground for this clock....so why does the reference design have it hooked up to VCC?