analog_ambi

Member level 1

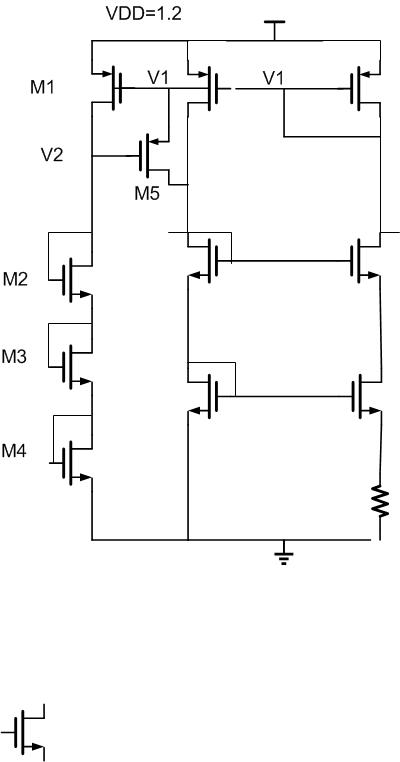

M1-M5 constitute startup circuit for the self bias refernce. VDD is 1.2 and V1 is usuall 700mV. M1 is sized for current=30nA.

After circuit startsup V2 is 1v and M1 goes to triode, M5 turns off. Is M1 going to triode after startup a problem?

After circuit startsup V2 is 1v and M1 goes to triode, M5 turns off. Is M1 going to triode after startup a problem?