tweekzilla

Newbie level 6

Hi,

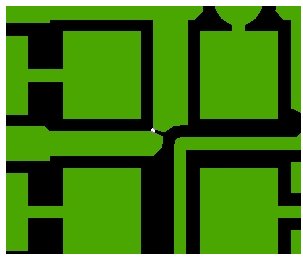

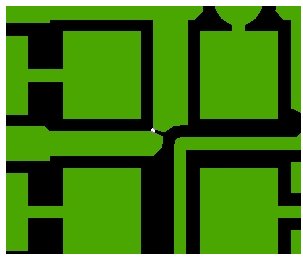

I'm doing a final copper pour (no net connection) to the top and bottom of a 6-layer board in Altium. The copper pour tends to leave small feature (gaps) as seen below no matter how much I tune the pour algorithm. These gaps then get flagged in freeDFM for advanced circuits - Some questions:

1) Do these small gaps really matter in manufacture when it's an unconnected copper plane?

2) Is there a way in Altium to get it to recognize these errors in the design check? It doesn't seem to care about them and I'd rather not have to upload every time to check for these gaps

3) Is there a way to stop Altium from leaving these gaps when doing the pour?

Thanks!

Ross

I'm doing a final copper pour (no net connection) to the top and bottom of a 6-layer board in Altium. The copper pour tends to leave small feature (gaps) as seen below no matter how much I tune the pour algorithm. These gaps then get flagged in freeDFM for advanced circuits - Some questions:

1) Do these small gaps really matter in manufacture when it's an unconnected copper plane?

2) Is there a way in Altium to get it to recognize these errors in the design check? It doesn't seem to care about them and I'd rather not have to upload every time to check for these gaps

3) Is there a way to stop Altium from leaving these gaps when doing the pour?

Thanks!

Ross