SeriousTyro

Member level 2

- Joined

- Apr 5, 2010

- Messages

- 49

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,288

- Activity points

- 1,620

I'm having troubling understanding how the sense amplifier and DRAM Cell works.

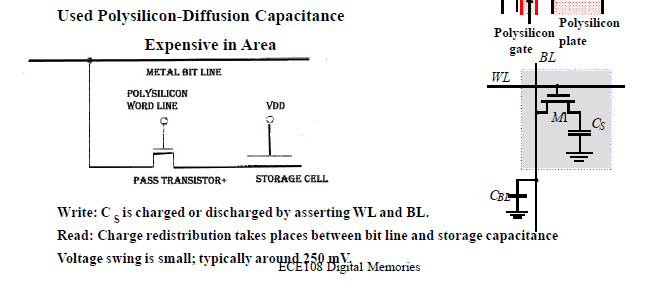

I understand how the write works. If you want to write high, you set WL and BL to high which will charge the storage capacitor.

I don't understand how read works. During the time before the capacitor can fully dissipate, you can read BL?

Whats C_BL for?

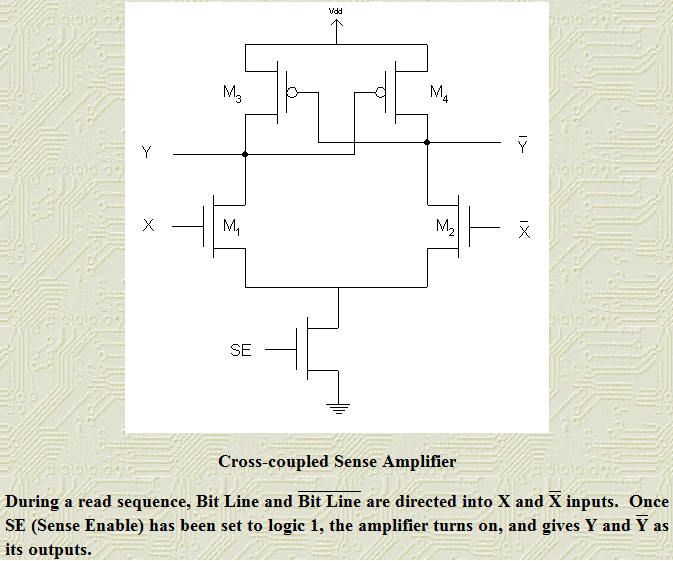

I can't seem to follow the circuit. I have a scenario where SE is high. Bit Line is high and Y is low but I am unable to follow the circuit.

How does this circuit work when outputting high and low?

Thanks

I understand how the write works. If you want to write high, you set WL and BL to high which will charge the storage capacitor.

I don't understand how read works. During the time before the capacitor can fully dissipate, you can read BL?

Whats C_BL for?

I can't seem to follow the circuit. I have a scenario where SE is high. Bit Line is high and Y is low but I am unable to follow the circuit.

How does this circuit work when outputting high and low?

Thanks