daisyzari

Junior Member level 3

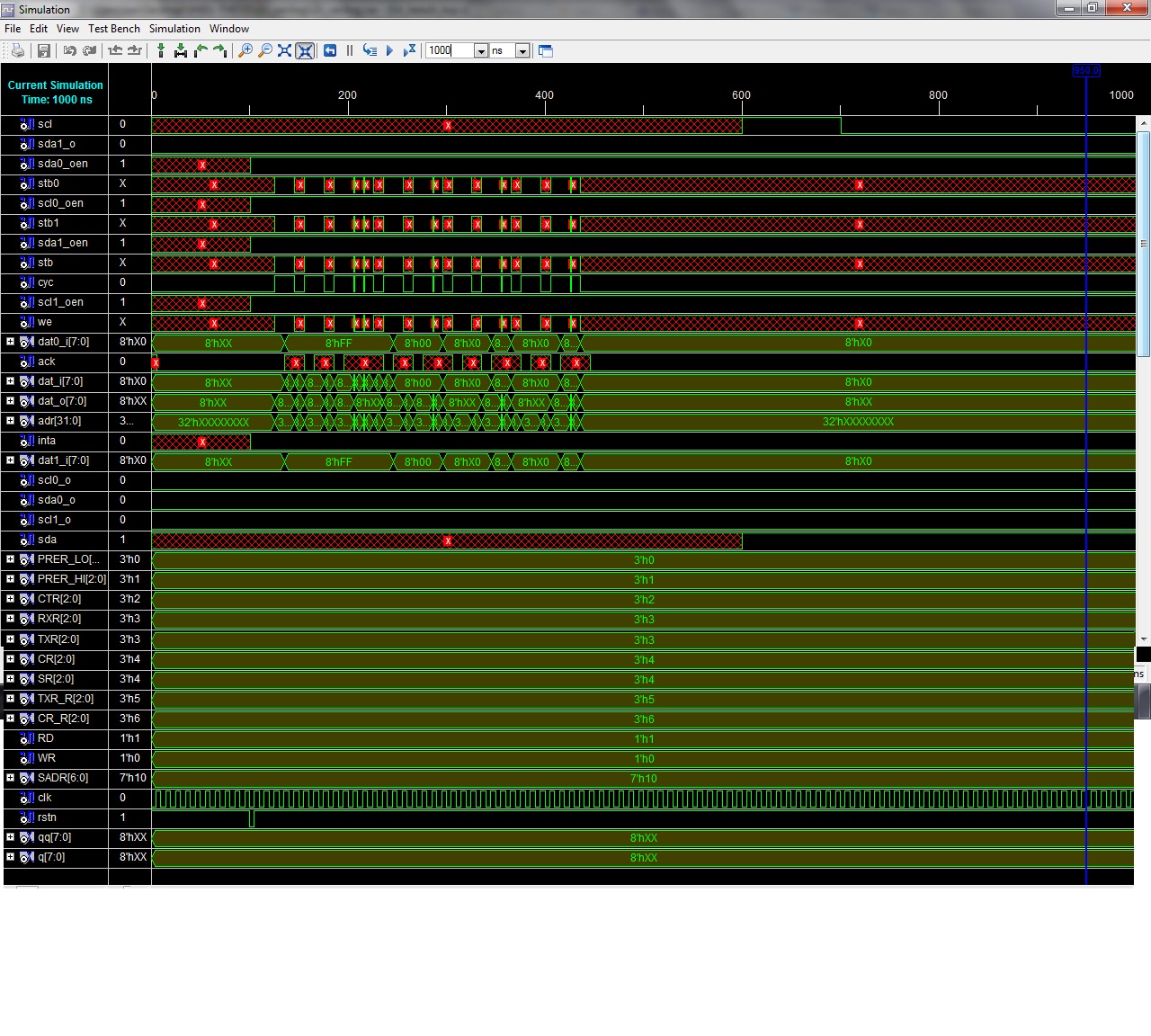

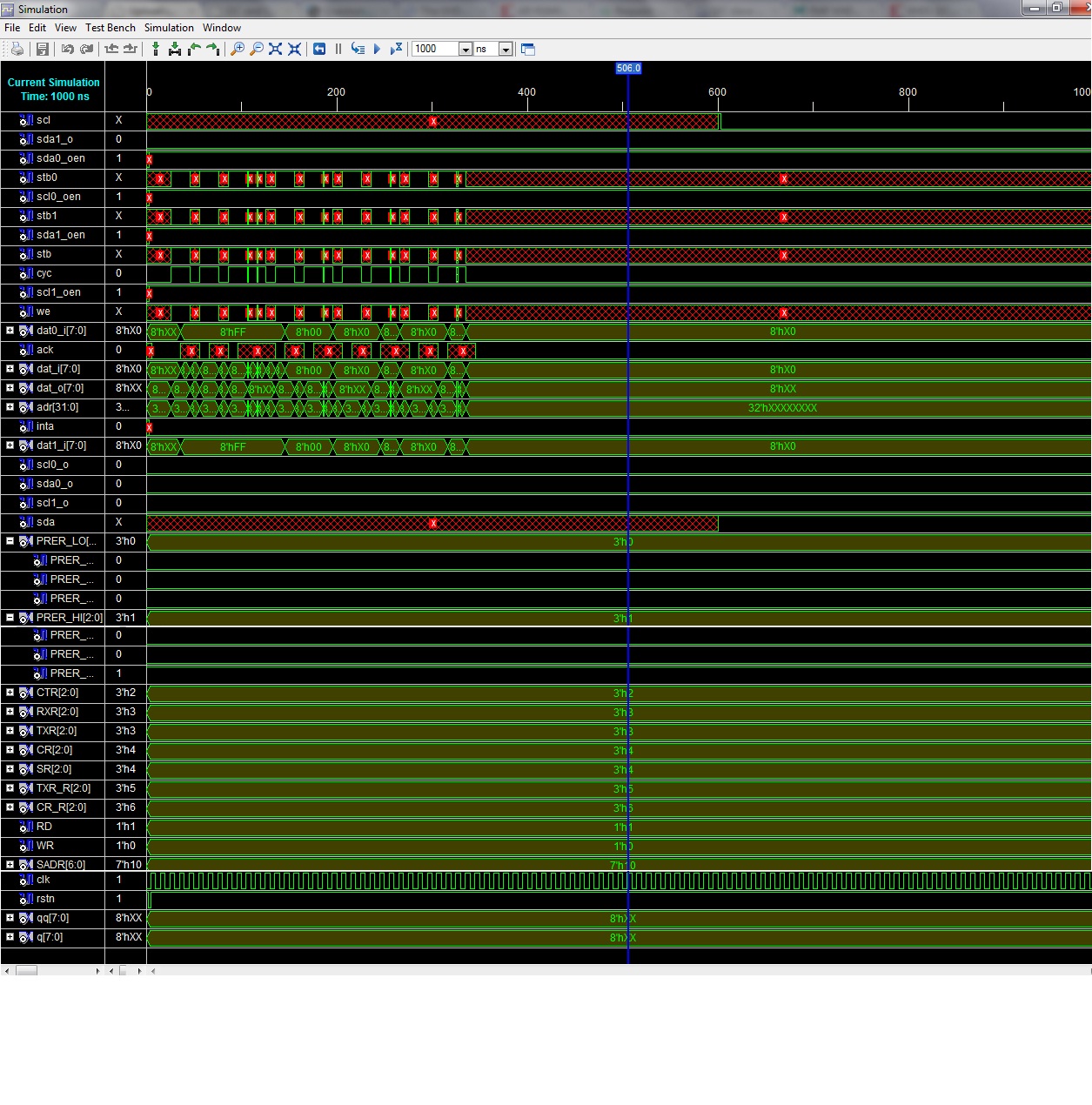

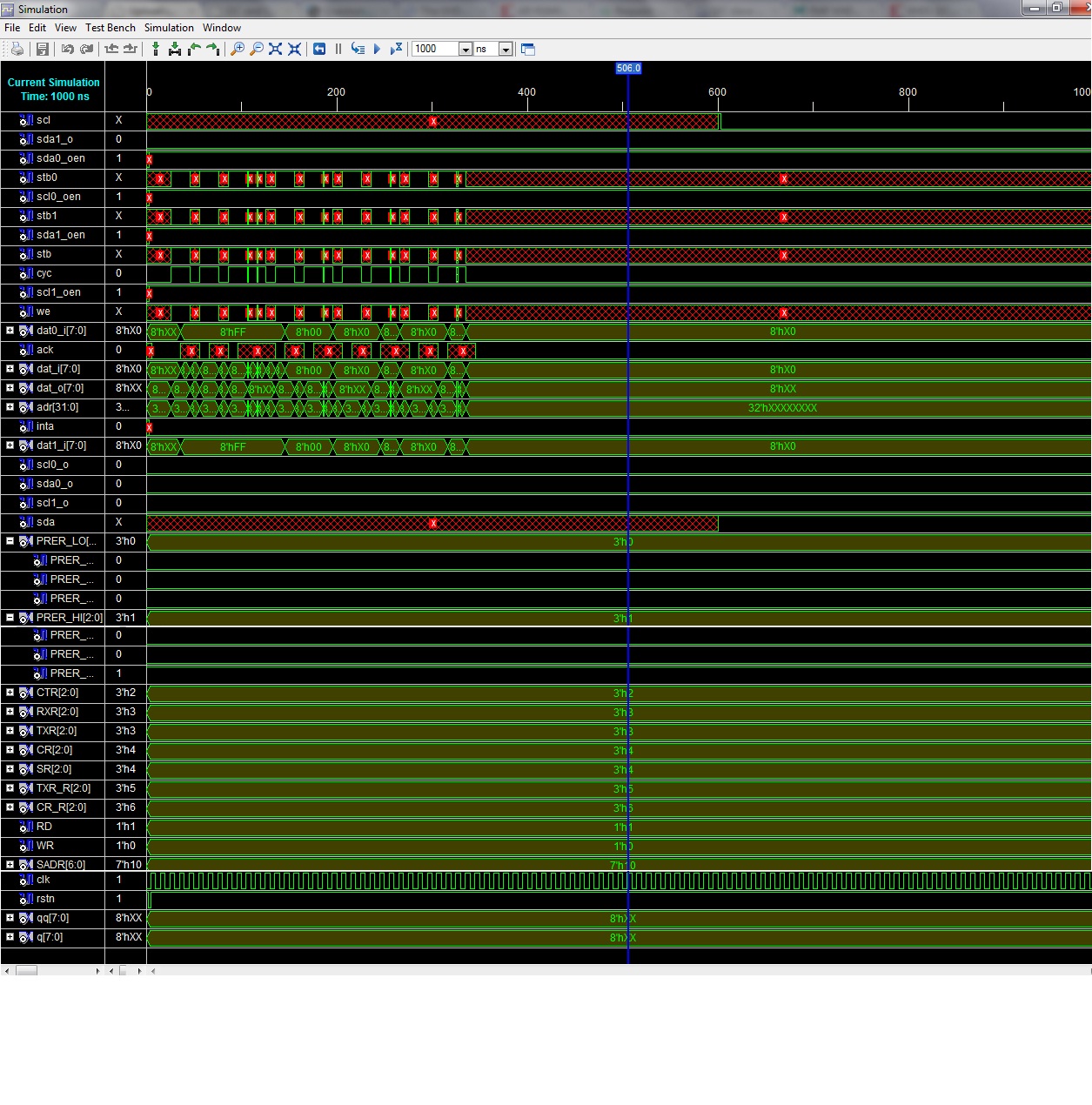

we tried simulating an I2C verilog code in Xilinx. But then, it seems that the output waveform is not good. we really need help in understanding what's wrong with the simulation/output waveform. I attached the code and the waveform is shown below:

Thank you

Thank you