raghuvlsi

Member level 1

hi ,

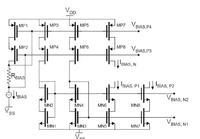

I raghu would like to design voltage regulator with an improved fast transient response.i have attached my base paper.Can any one guide me how to design from base level of voltage regulator and how to design individual blocks initially according to my base paper design with specs of each block.

Please tell me what are the specifications i need to take initially based on my base paper design.Right now i planned to design error amplifier which is used "single ended folded cascode OTA" for traditional LDO as mentioned in base paper.

Thanq

I raghu would like to design voltage regulator with an improved fast transient response.i have attached my base paper.Can any one guide me how to design from base level of voltage regulator and how to design individual blocks initially according to my base paper design with specs of each block.

Please tell me what are the specifications i need to take initially based on my base paper design.Right now i planned to design error amplifier which is used "single ended folded cascode OTA" for traditional LDO as mentioned in base paper.

Thanq