fuxinmingming

Member level 1

Hi guys,

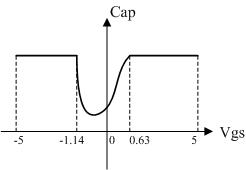

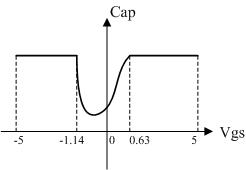

i simulated the current through moscap to get cap's value. Here is the curve:

Can someone pls explain?

1. Why the curve is not symmetrical with axis y(Vgs left=-1.14V, Vgs right=0.63V, why Vgs left \neq Vgs right) ?

2. I know the maximum value is W\cdot L\cdot Cox, but what's the minimum value of the cap? Can i calculate it?

Regards

Ming

---------- Post added at 07:28 ---------- Previous post was at 07:26 ----------

2. I know the maximum value is W\cdot L\cdot Cox, but what's the minimum value of the cap? Can i calculate it?

sorry for the mistake, it's WLCox.

i simulated the current through moscap to get cap's value. Here is the curve:

Can someone pls explain?

1. Why the curve is not symmetrical with axis y(Vgs left=-1.14V, Vgs right=0.63V, why Vgs left \neq Vgs right) ?

2. I know the maximum value is W\cdot L\cdot Cox, but what's the minimum value of the cap? Can i calculate it?

Regards

Ming

---------- Post added at 07:28 ---------- Previous post was at 07:26 ----------

2. I know the maximum value is W\cdot L\cdot Cox, but what's the minimum value of the cap? Can i calculate it?

sorry for the mistake, it's WLCox.