kellyza

Member level 1

Hi all,

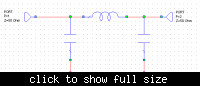

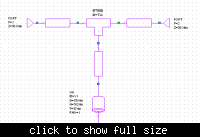

I would like to ask anyone out there on how to draw footprint of discrete component (both axial and chip type) using microwave office.

For your info, I'm designing a circuit consisting discrete elements such as transistor, resistor and capacitor. I'm not really sure how to draw the footprint using MWO. I have all the dimensions as in datasheet provided.

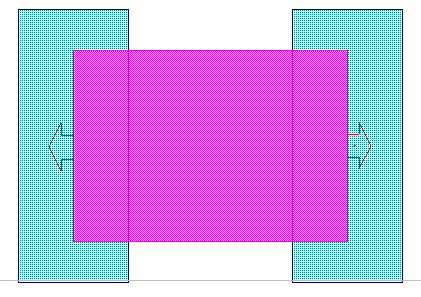

One more question, as in the layout, does it require some sort of stab or fan to connect the wire/txn line with the discrete component. I could not find that in MWO elements.

Thanks in advance.

I would like to ask anyone out there on how to draw footprint of discrete component (both axial and chip type) using microwave office.

For your info, I'm designing a circuit consisting discrete elements such as transistor, resistor and capacitor. I'm not really sure how to draw the footprint using MWO. I have all the dimensions as in datasheet provided.

One more question, as in the layout, does it require some sort of stab or fan to connect the wire/txn line with the discrete component. I could not find that in MWO elements.

Thanks in advance.