sunnymeharwal

Newbie level 4

- Joined

- Sep 15, 2008

- Messages

- 6

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,349

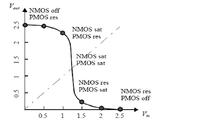

From CMOS Inverter voltage transfer characteristics, we see that nMOS transistor switches from Cut-Off (region - A ) to Saturation (region - B )

and pMOS transistor switches from Saturation (region - D ) to Cut-Off (region - E ).

This can be explained by equations and by calculating the Vds which satisfies the above conditions.

But nMOS and pMOS transistors are practical devices,

So, in case of switching of nMOS from Cut-Off (region - A ) to Saturation (region - B ) the linear region should come in between.

Is the linear region comes in between or

nMOS does not enter into linear region even for a very short interval of time ?

Thanks[/b]

and pMOS transistor switches from Saturation (region - D ) to Cut-Off (region - E ).

This can be explained by equations and by calculating the Vds which satisfies the above conditions.

But nMOS and pMOS transistors are practical devices,

So, in case of switching of nMOS from Cut-Off (region - A ) to Saturation (region - B ) the linear region should come in between.

Is the linear region comes in between or

nMOS does not enter into linear region even for a very short interval of time ?

Thanks[/b]